#### FOREWORD

This is the final report for the Solid State Matrix Program, which was conducted from 1 April 1962 to 12 July 1963 under Contract Nr. AF33(657) - 8688, Project Nr. 8128, and Task Nr. 812806 for the Aeronautical Systems Division, Air Force Systems Command, United States Air Force. It was under the direction of the AF Aero-Propulsion Laboratory with Mr. Lester E. Schott as RTD project engineer.

The program was conducted at the Alexandria Laboratories of the Research and Development Division of AMF. It was assigned to the Systems Engineering Department under Mr. Saul H. Silver. It was directed by Mr. R. N. Stock as AMF project engineer and was performed by Mr. R. N. Stock and Mr. R. W. Powell. Mr. S. Rubin of the Alexandria Laboratories and Mr. R. W. Townsend of the Springdale Laboratories acted as technical consultants in establishing the logic design. Mr. L. Mittelman, senior electronic engineer, Alexandria Laboratories, contributed many helpful suggestions to the circuit design effort. This report has been written by Mr. R. N. Stock and Mr. R. W. Powell.

In the event of a conflict between data presented in this report and data presented in any earlier report issued under this program, the data of this report shall prevail.

#### ABSTRACT

This report describes an engineering study and development effort to produce efficient and practical solid state transmission links (i.e., electrical power control and distribution systems). They were to be suitable for advanced aerospace vechicles and to have higher reliability than the conventional electromechanical transmission links used in present-day aircraft.

Two transmission links of the F-106B were re-designed as solid state systems to demonstrate the feasibility of solid state transmission links. Components were not replaced on a one-for-one basis. Instead, an overall functional analysis was made and then the logic system was designed so that solid state devices would be employed most efficiently. In particular, control and protection functions were performed by a single power switch. Also, all logic was performed at a low level. However, the operational functions of the original systems were retained.

The solid state systems used controlled rectifiers and power transistors as power handling devices. Control circuits were implemented with T.I. Solid Circuits, the G.E. silicon controlled switch (3N60), the unijunction transistor (2N491B), a compound transistor (2N2223), and a complementary pair of transistors (2N718/2N722). An interesting aspect of the systems was that relatively few types of devices were needed to implement a variety of functions. These functions included 4 areas: (1) power switches; (2) control circuits; (3) power supplies; and (4) circuit breakers.

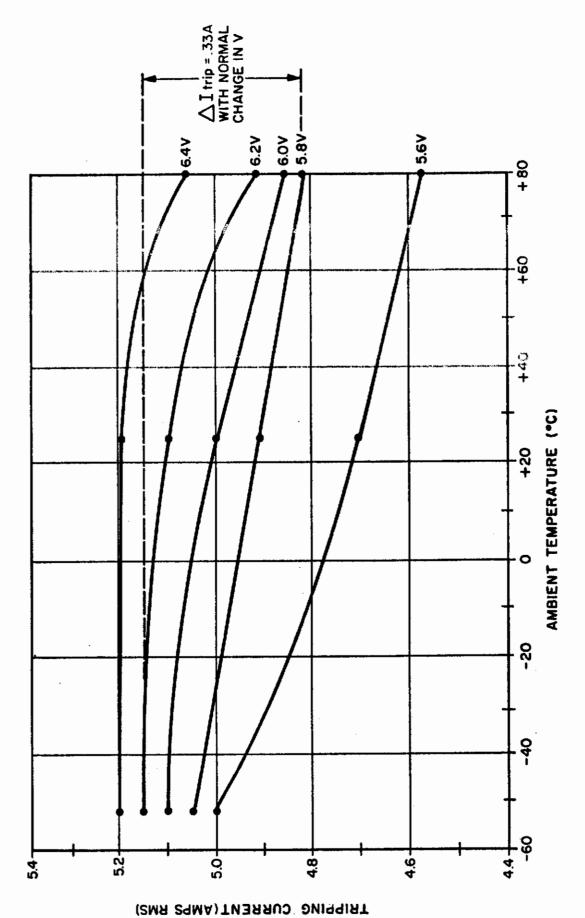

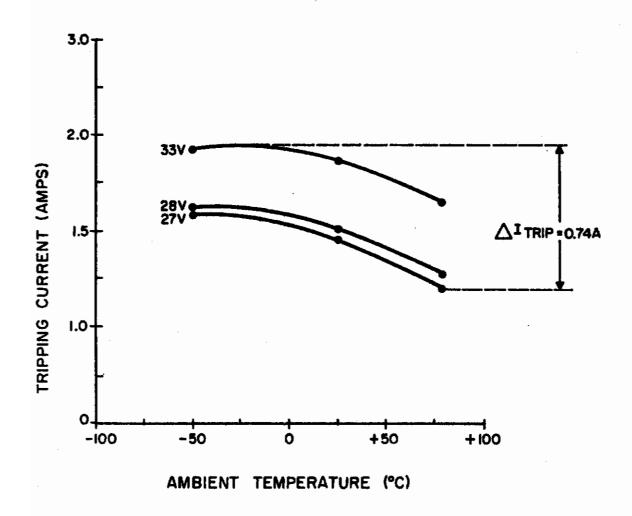

The solid state systems were tested over the temperature range of -55°C to +80°C. Results were good; however, some alternate circuits were designed after the satisfactory completion of system tests. This was done because it became apparent that significant improvements could be made with relatively little effort. For example, the original dc overload circuit contained 42 parts and exhibited a trip current variation of 20% over the temperature range of -55°C to +80°C; the alternate dc overload circuit contained 23 parts and exhibited a trip current variation of only 1% over the same temperature range.

It was concluded that definite advantages can be provided by the application of solid state techniques to transmission links for advanced aerospace vehicles. However, 2 key problems are voltage transients and power switch cooling. By virtue of the techniques developed, applied, and then clearly presented in the design manual, this program furnished a sound

basis for the future development of operational solid state transmission links for advanced aerospace vehicles.

This technical documentary report has been reviewed and is approved:

G.W. SHERMAN, Chief

Aerospace Power Division AF Aero-Propulsion Laboratory

## TABLE OF CONTENTS

| Sec | tion  |         |                                   | Page |

|-----|-------|---------|-----------------------------------|------|

|     | INTRO | DUCTIO  | ON                                | 1    |

| 1.  | ANAL  | YSIS OF | SCHEMATICS                        | 4    |

|     | 1. 1  | DC Po   | wer System                        | 4    |

|     |       | 1. 1. 1 | Description of Operation          | 5    |

|     |       | 1. 1. 2 | Definition of System Bounds       | 11   |

|     |       | 1. 1. 3 | System Loads                      | 15   |

|     | 1.2   | Anti-io | ce System                         | 15   |

|     |       | 1.2.1   |                                   | 16   |

|     |       | 1.2.2   | Definition of System Bounds       | 21   |

|     |       | 1.2,3   | System Loads                      | 22   |

| 2.  | EVAL  | UATION  | OF SEMICONDUCTOR DEVICES          | 25   |

|     | 2. 1  | Power   | Handling Devices                  | 26   |

|     |       |         | Controlled Rectifiers             | 26   |

|     |       | 2.1.2   | Power Transistors                 | 27   |

|     |       | 2. 1. 3 | Rectifiers                        | 29   |

|     | 2. 2  | Contro  | ol Circuit Devices                | 29   |

|     |       | 2.2.1   | Discrete Devices                  | 29   |

|     |       | 2.2.2   | Functional Devices                | 35   |

| 3.  | TEMP  | ERATU   | RE RANGE                          | 40   |

|     | 3. 1  | Anticip | pated Thermal Environment         | 40   |

|     |       | 3.1.1   | Earth                             | 40   |

|     |       | 3.1.2   | Space                             | 41   |

|     |       | 3.1.3   | Planets                           | 41   |

|     |       | 3.1.4   | Re-entry                          | 42   |

|     |       | 3.1.5   | Typical Requirements              | 42   |

|     |       | 3.1.6   | Temperature Limits                | 43   |

|     | 3. 2  | Tempe   | rature Range of Present Devices   | 43   |

|     | 3.3   | Tempe   | rature Range of Present Circuitry | 43   |

|     | 3. 4  | Selecte | ed Temperature Range              | 44   |

| Sec | tion  |                                                    | Page |

|-----|-------|----------------------------------------------------|------|

|     | 3.5   | Effects of the Actual Thermal Environment          | 45   |

| 4.  | LOGIC | AND CIRCUIT DESIGN                                 | 46   |

|     | 4. 1  | Design Philosophy                                  | 46   |

|     |       | 4.1.1 Logic Design                                 | 46   |

|     |       | 4.1.2 Control Circuit and Power Switch Design      | 47   |

|     |       | 4.1.3 Overload Protection                          | 49   |

|     |       | 4. 1. 4 Parts Data                                 | 49   |

|     | 4.2   | DC Power System                                    | 52   |

|     |       | 4. 2. 1 Abstract Logic                             | 52   |

|     |       | 4. 2. 2 Detailed Logic                             | 54   |

|     |       | 4. 2. 3 Circuit Design                             | 59   |

|     |       | 4. 2. 4 Description of Operation - DC Power System | 80   |

|     | 4.3   | Anti-ice System                                    | 83   |

|     |       | 4.3.1 Abstract Logic                               | 83   |

|     |       | 4.3.2 Detailed Logic                               | 87   |

|     |       | 4.3.3 Circuit Design                               | 92   |

|     |       | 4.3.4 Description of Operation                     | 105  |

| 5.  | SPECI | FICATION, SOLID STATE MATRIX                       | 113  |

|     | 5. 1  | Scope                                              | 113  |

|     | 5. 2  | Applicable Documents                               | 113  |

|     | 5.3   | Requirements                                       | 113  |

|     |       | 5. 3. 1 Electrical                                 | 113  |

|     |       | 5. 3. 2 Temperature                                | 117  |

|     |       | 5.3.3 Design Criteria                              | 118  |

|     | 5.4   | Experimental Evaluation Procedure                  | 119  |

|     |       | 5. 4. 1 Purpose                                    | 119  |

|     |       | 5.4.2 Testing Approach                             | 119  |

|     |       | 5. 4. 3 Test Equipment                             | 120  |

|     |       | 5. 4. 4 DC Control Section Tests                   | 121  |

|     |       | 5. 4. 5 Experimental TR Control Section            | 125  |

|     |       | 5. 4. 6 Experimental Anti-ice System               |      |

| 6.  | EXPE  | RIMENTAL EVALUATION DATA                           | 131  |

|     | 6. 1  | DC Control Section                                 | 131  |

| Section | ı                  |                                                 | Page |

|---------|--------------------|-------------------------------------------------|------|

|         | 6. 1. 1<br>6. 1. 2 | DC Power Regulator (VR1, VR2)                   | 136  |

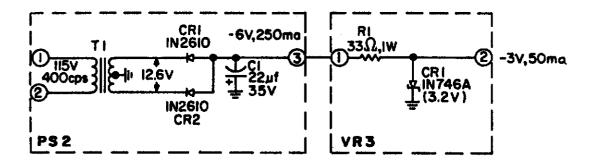

|         | 0. 1. 2            | Negative Power Supply (PS2) and Regulator (VR3) | 136  |

|         | 6. 1. 3            | Chute Deploy DC Overload Circuit                | 140  |

|         | 6. 1. 4            | X2a, X2b, and Associated Amplifiers             |      |

|         |                    | (AP1, AP2)                                      | 148  |

|         | 6. 1. 5            | Battery to Essential Bus Switch, X3             | 148  |

|         | 6. 1. 6            | Voltage Sensor (VS1, VS2)                       | 157  |

|         | 6. 1. 7            | DC Control Section Storage Test                 | 157  |

| 6.      | 2 Experi           | mental TR Control Section                       | 157  |

|         | 6.2.1              | Three Phase AC to DC Power Supply (PS1)         |      |

|         |                    | and Regulators (VR4, VR5)                       | 157  |

|         | 6. 2. 2            | AC Switch Firing Circuit                        | 157  |

|         | 6.2.3              | AC Switch                                       | 159  |

|         | 6. 2. 4            | AC Overload Detection Circuit                   | 162  |

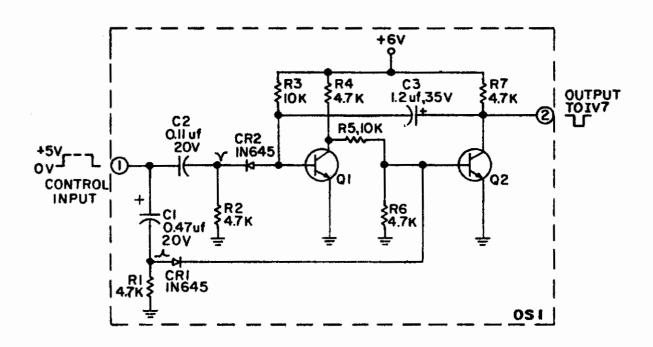

|         | 6.2.5              | Delay Gate Multivibrator                        | 162  |

|         | 6. 2. 6            | X4 and X5 Firing Circuits                       | 166  |

|         | 6. 2. 7            | X4 and X5 Power Switches                        | 167  |

|         | 6. 2. 8            | Experimental TR Control Section Storage Test    | 168  |

| 6.      | 3 Experi           | mental Anti-ice System                          | 168  |

|         | 6.3.1              | Time Delay Circuits                             | 168  |

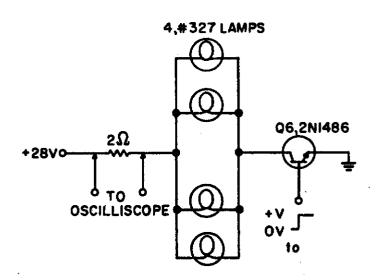

|         | 6.3.2              | Warning Light System                            | 168  |

|         | 6.3.3              | Warning Light Overload Circuit                  | 170  |

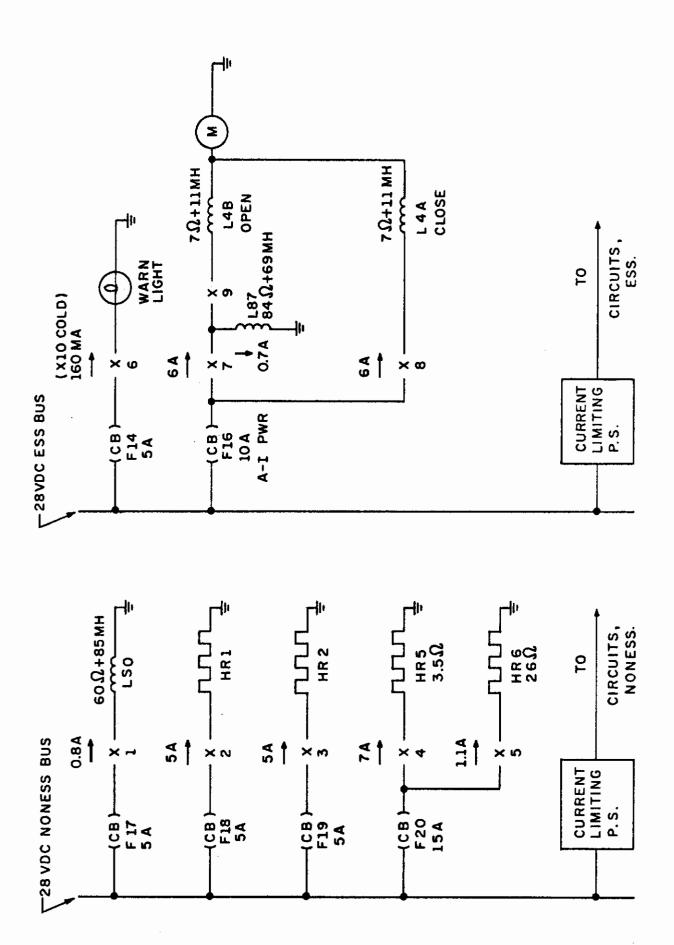

|         | 6.3.4              | Motor-driven Valve Circuit                      | 170  |

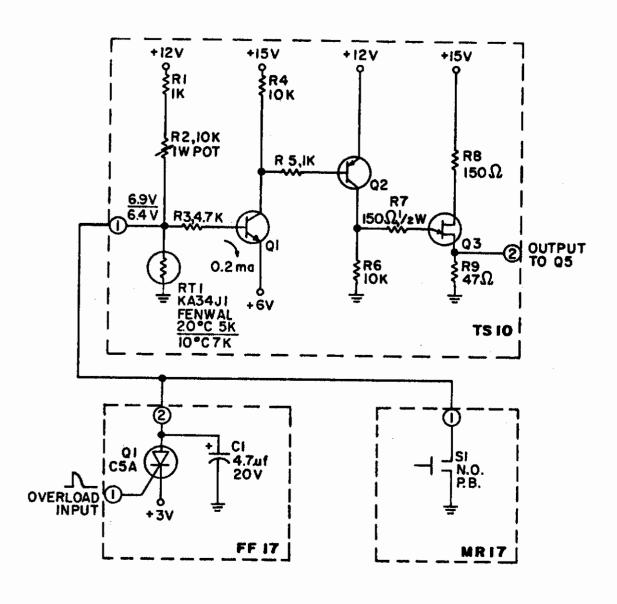

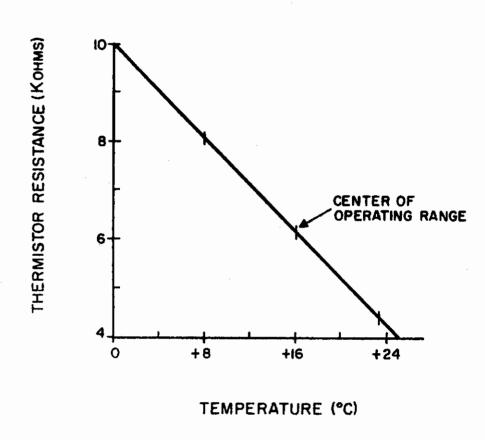

|         | 6.3.5              | Temperature Sensor (TS10)                       | 176  |

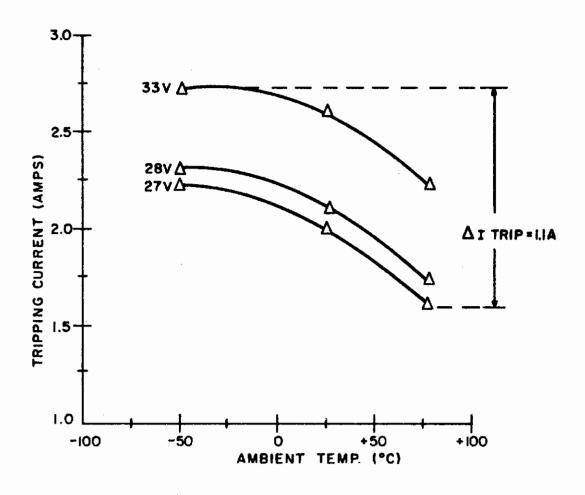

|         | 6.3.6              | Case Heater Overload Circuit                    | 178  |

|         | 6.3.7              | Experimental Anti-ice Section Storage Test      | 181  |

| 7. AI   | LTERNATE           | CIRCUITS                                        | 182  |

| 7.      | l Altern           | ate Circuits from Original Design               | 182  |

|         | 7.1.1              | Phase Controlled Rectifier                      | 182  |

|         | 7.1.2              | TR Detection Circuit                            | 184  |

|         | 7.1.3              | Original AC Switch and Firing Circuit           | 184  |

| 7.      | 2 New A            | Iternate Circuits                               | 187  |

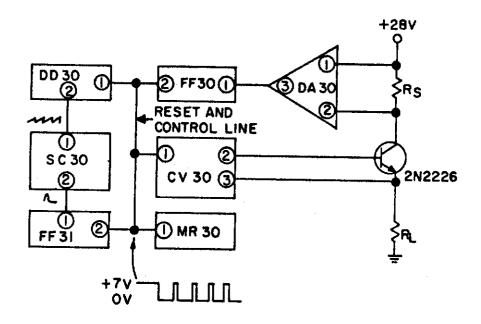

|         | 7.2.1              | DC to DC Power Converter, CV30                  | 187  |

|         | 7.2.2              | Emitter-Follower Power Switch                   | 189  |

|         | 7.2.3              | Improved DC Overload Circuit                    | 190  |

| Section |                                        |                                  | Page |

|---------|----------------------------------------|----------------------------------|------|

| 8.      | CONC                                   | LUSIONS AND RECOMMENDATIONS      | 199  |

|         | 8, 1                                   | Improvements to Designed Systems | 200  |

|         | 8. 2                                   | Solid State Transmission Links   | 200  |

|         |                                        | 8. 2. 1 Power Switches           | 200  |

|         |                                        | 8. 2. 2 Control Circuits         | 201  |

|         |                                        | 8. 2. 3 Power Supplies           | 202  |

|         |                                        | 8. 2. 4 Circuit Protectors       | 202  |

|         | 8.3                                    | Hybrid Systems                   | 203  |

|         | 8.4                                    | Special Applications             | 203  |

|         | ************************************** | WI BEGGEVELANTAL                 | 205  |

## LIST OF ILLUSTRATIONS

| Figure No. | <u>Title</u>                                               |     |  |

|------------|------------------------------------------------------------|-----|--|

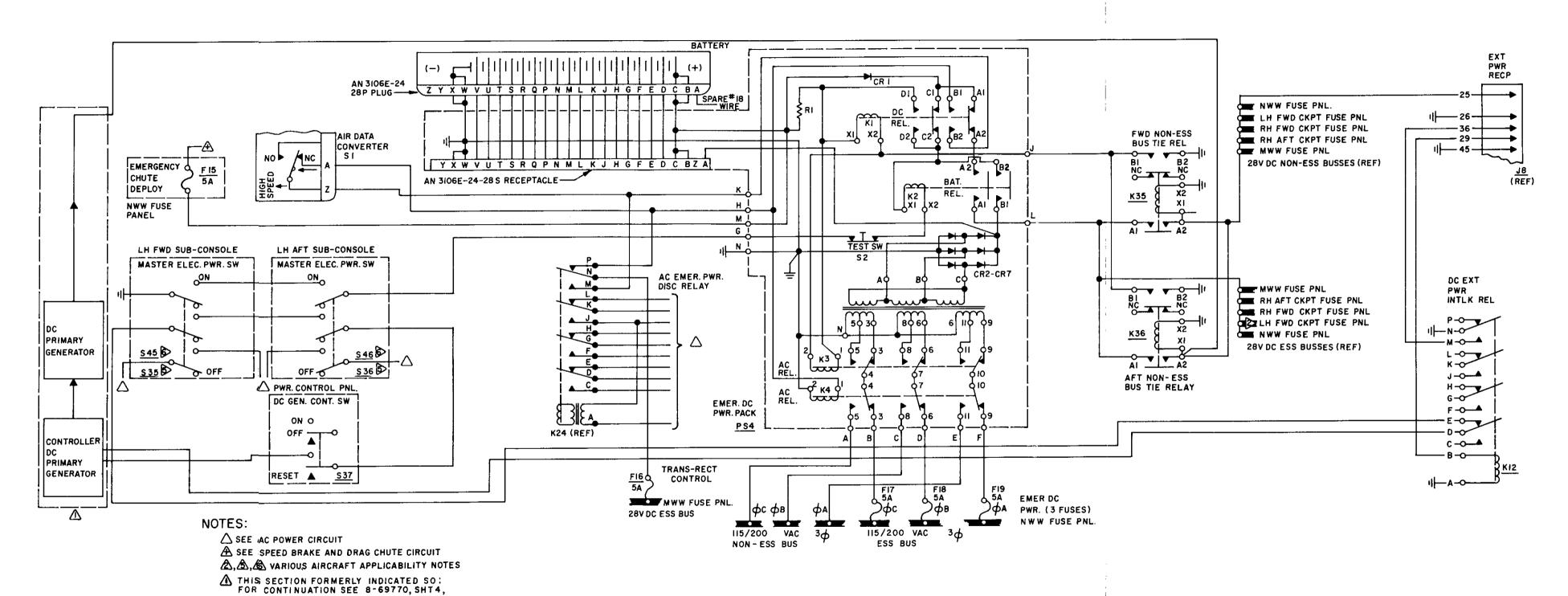

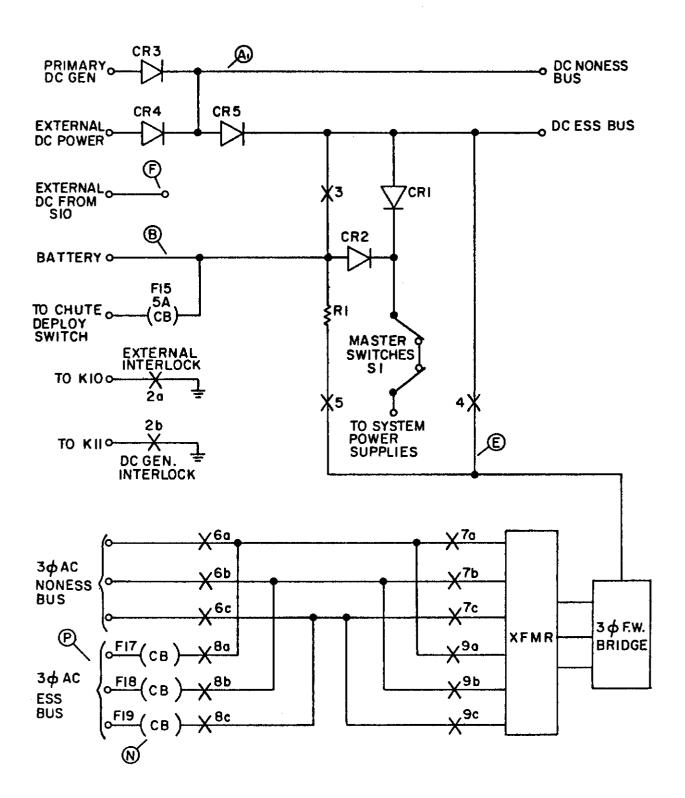

| 1          | Original DC Power Schematic                                | 6   |  |

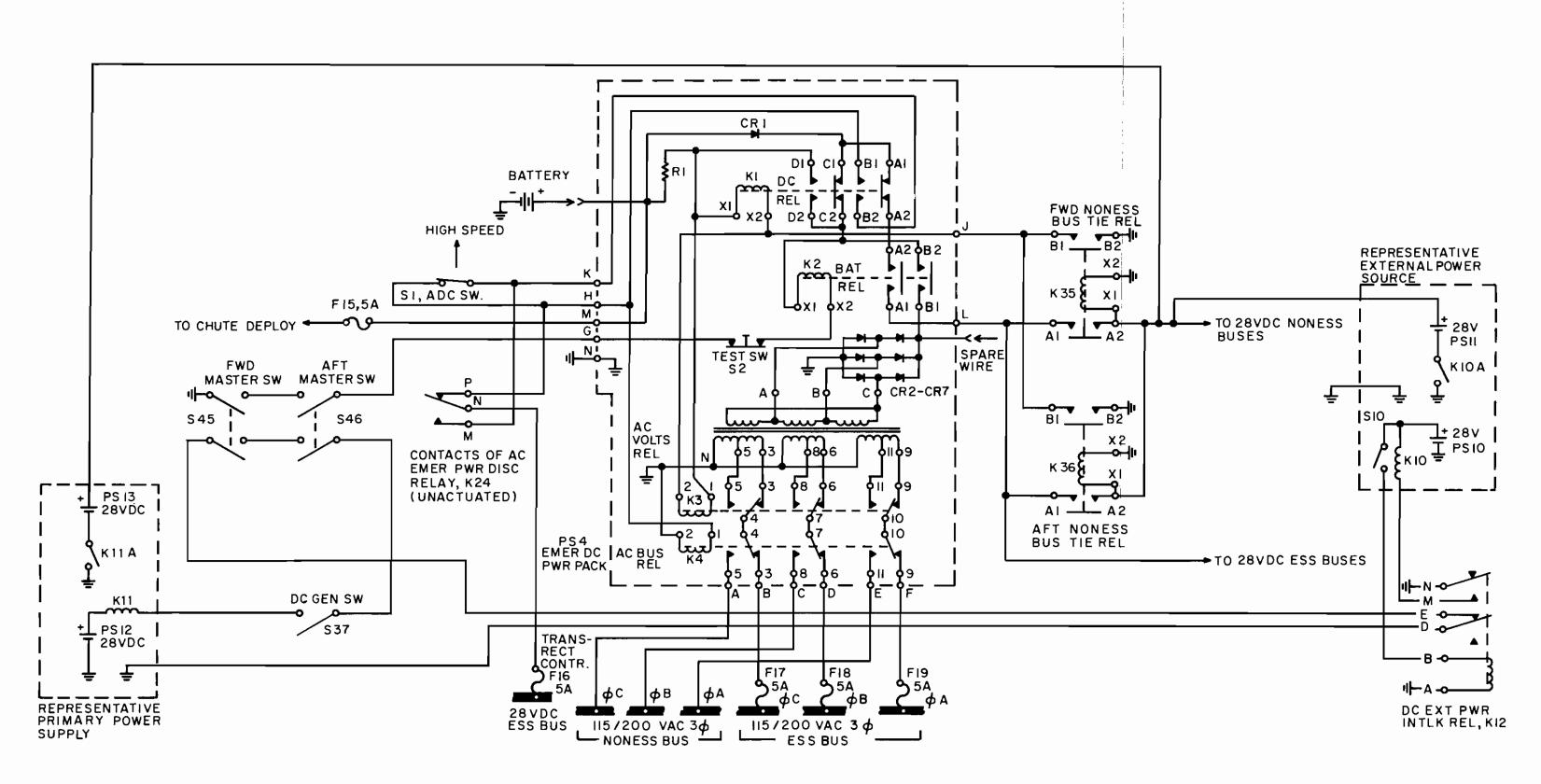

| 2          | Simplified DC Power Schematic                              | 13  |  |

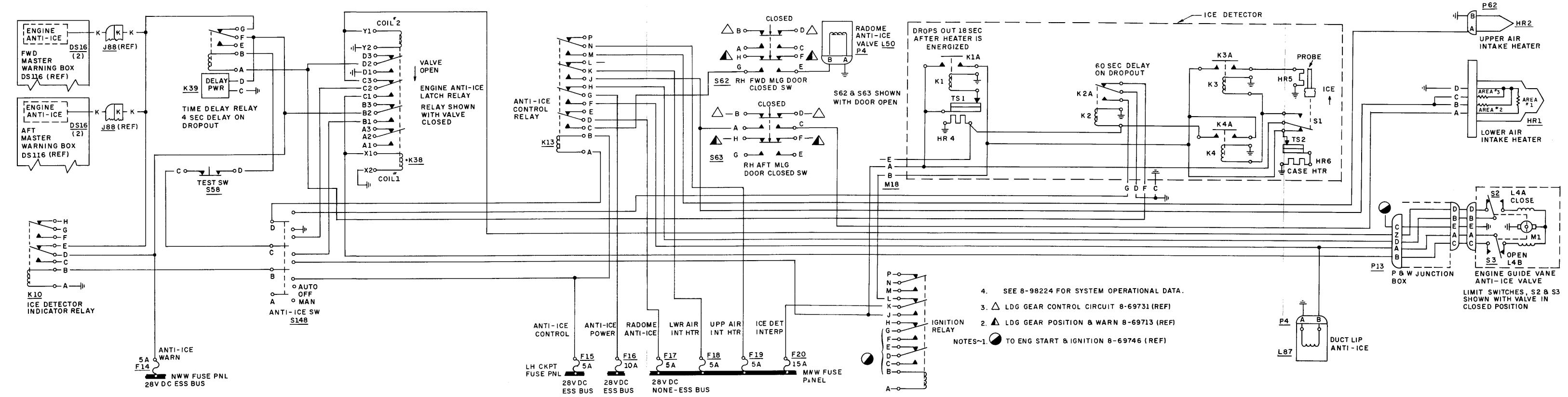

| 3          | Original Anti-ice Schematic                                | 14  |  |

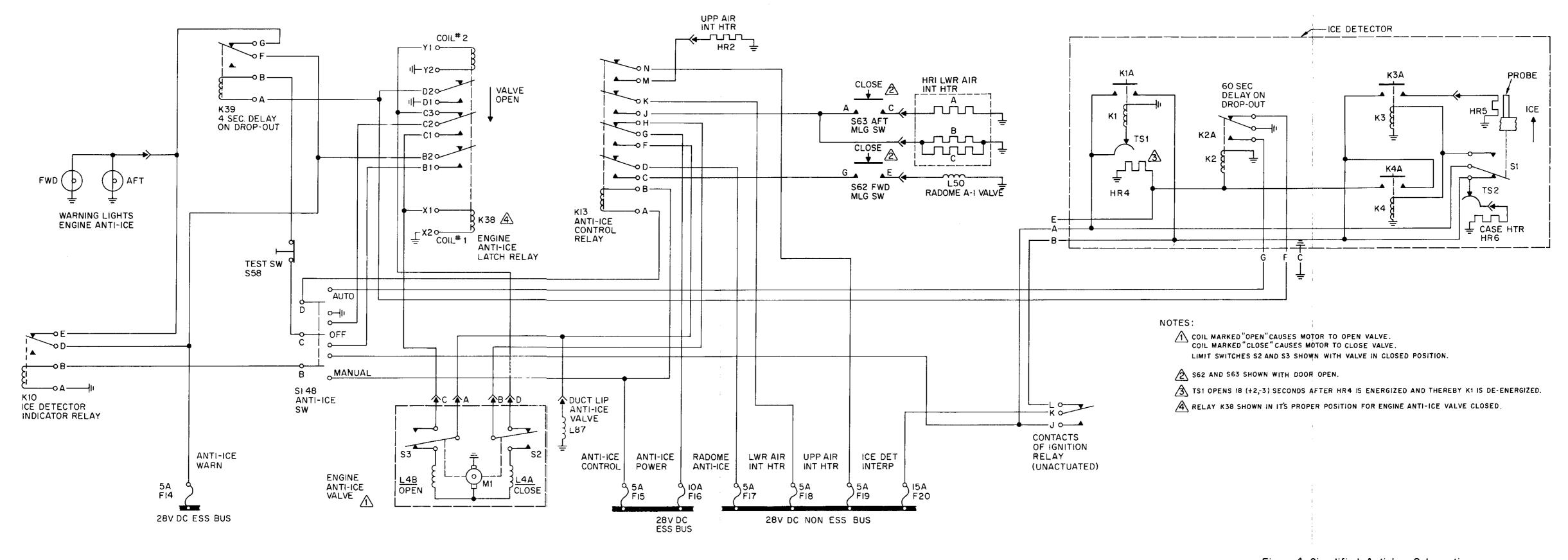

| 4          | Simplified Anti-ice Schematic                              | 24  |  |

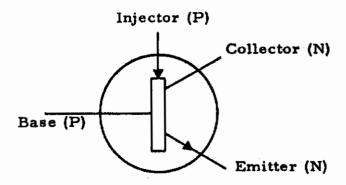

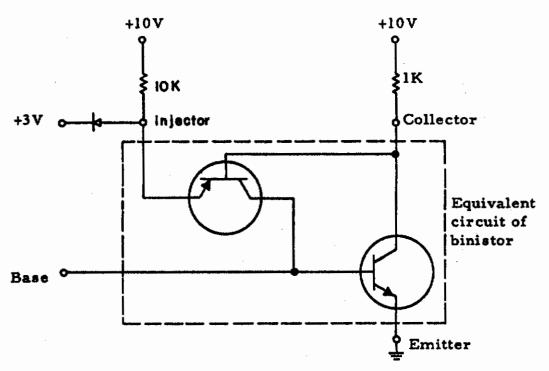

| 5          | The Binistor                                               | 32  |  |

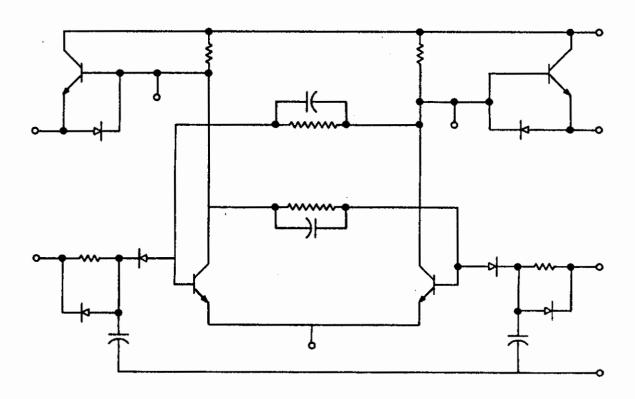

| 6          | Example of a Commercially Available Solid  Network         | 37  |  |

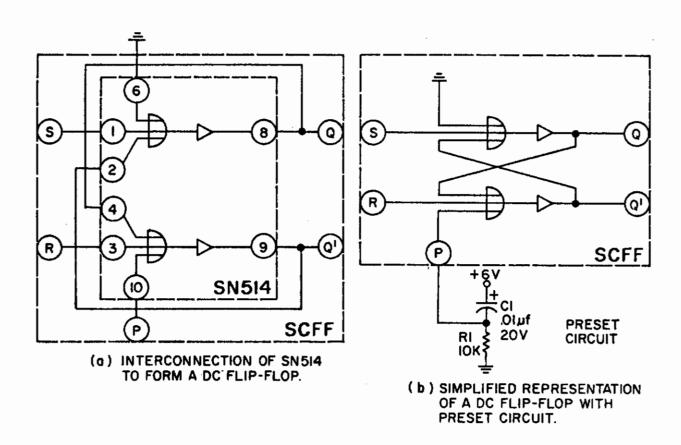

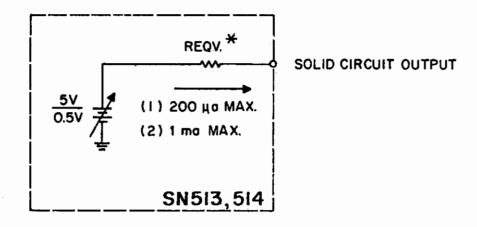

| 7          | Solid Circuit Flip-Flop and Equivalent Output Stage        | 48  |  |

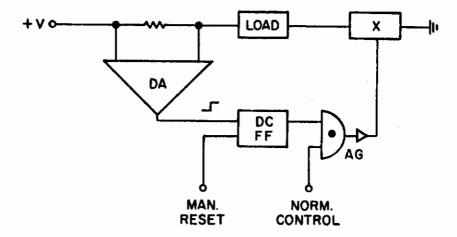

| 8          | DC Overload Protection Technique                           | 50  |  |

| 9          | Abstract Logic for Power Switches of the DC                | 30  |  |

| ,          | Power System                                               | 53  |  |

| 10         | Abstract Logic for Control of the DC Power                 |     |  |

|            | System                                                     | 56  |  |

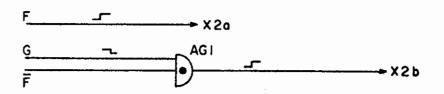

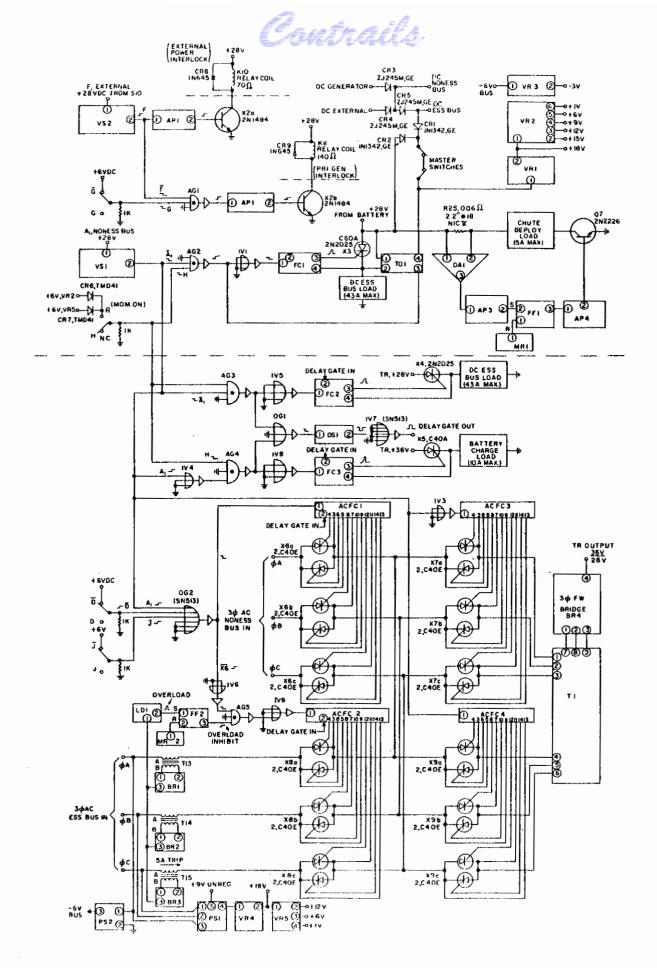

| 11         | Detailed Block Diagram of the DC Power System              | 57  |  |

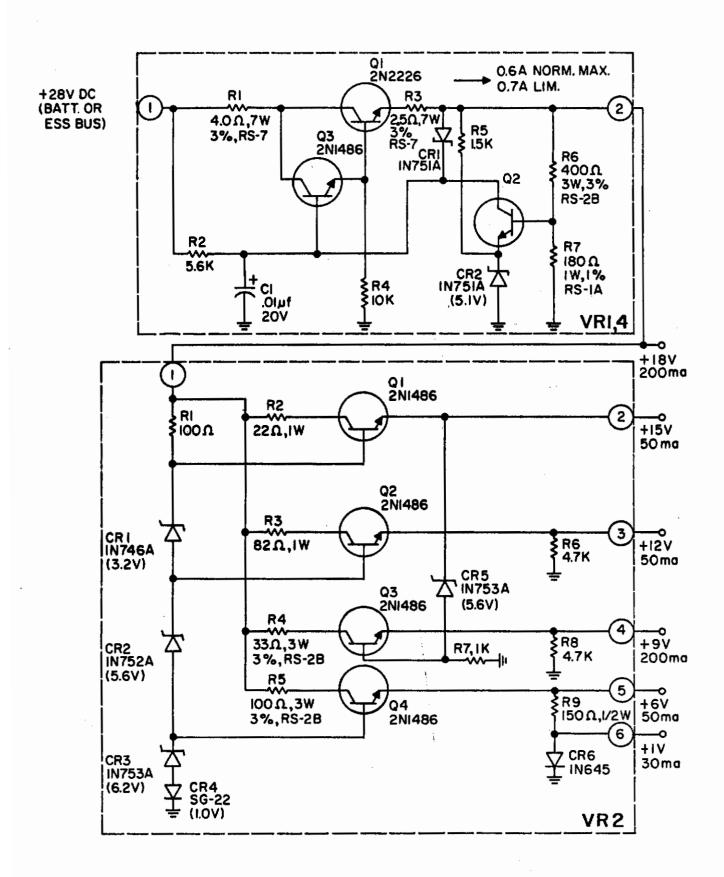

| 12         | Voltage Regulators (VRI, 2, 4)                             | 60  |  |

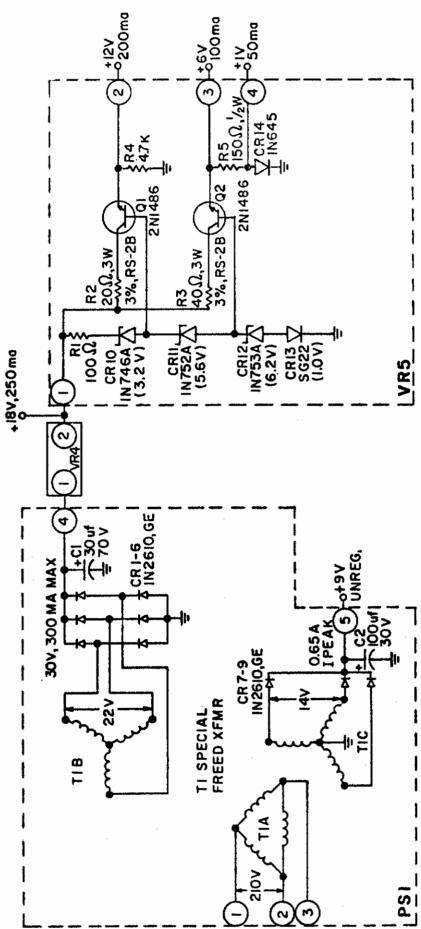

| 13         | AC to DC Power Supply and Regulator                        | 61  |  |

| 14         | Negative Power Supply and Regulator                        | 62  |  |

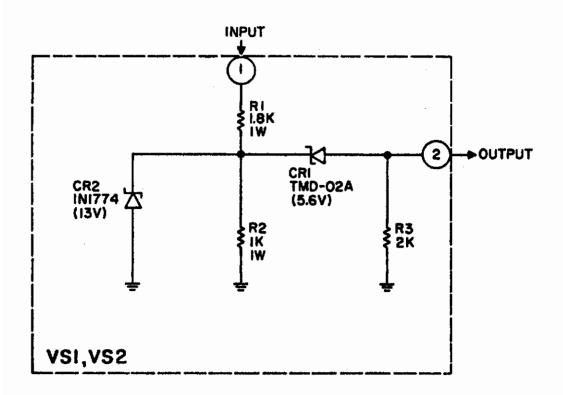

| 15         | Voltage Sensor                                             | 66  |  |

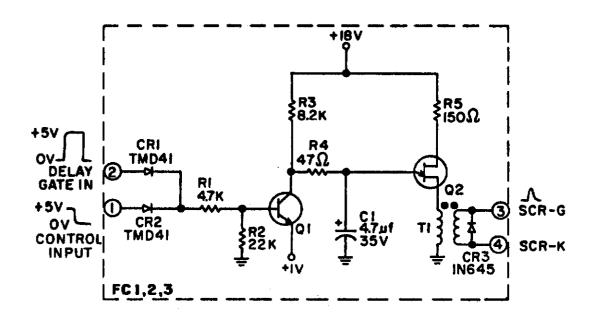

| 16         | SCR Firing Circuit                                         | 67  |  |

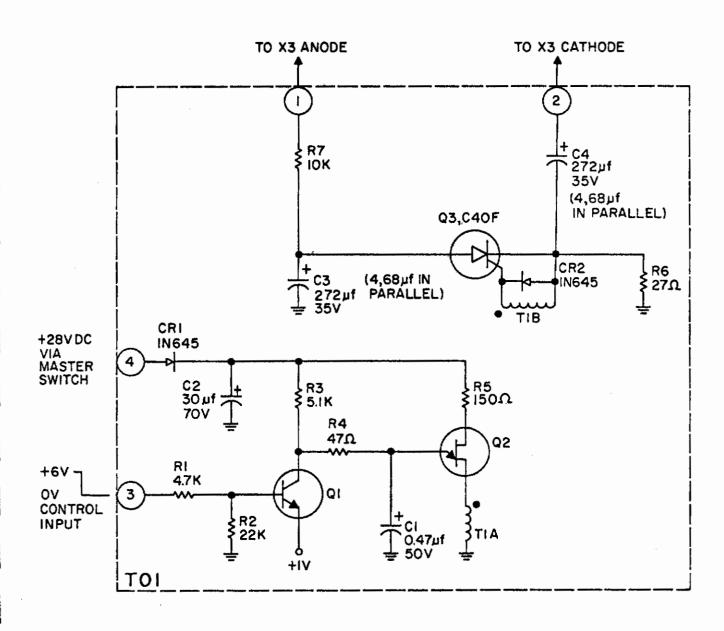

| 17         | X3 Turn-Off Circuit                                        | 69  |  |

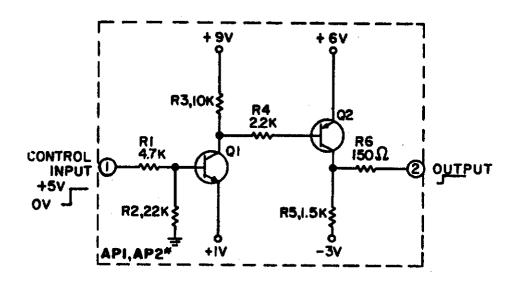

| 18         | Interlock Amplifier                                        | 70  |  |

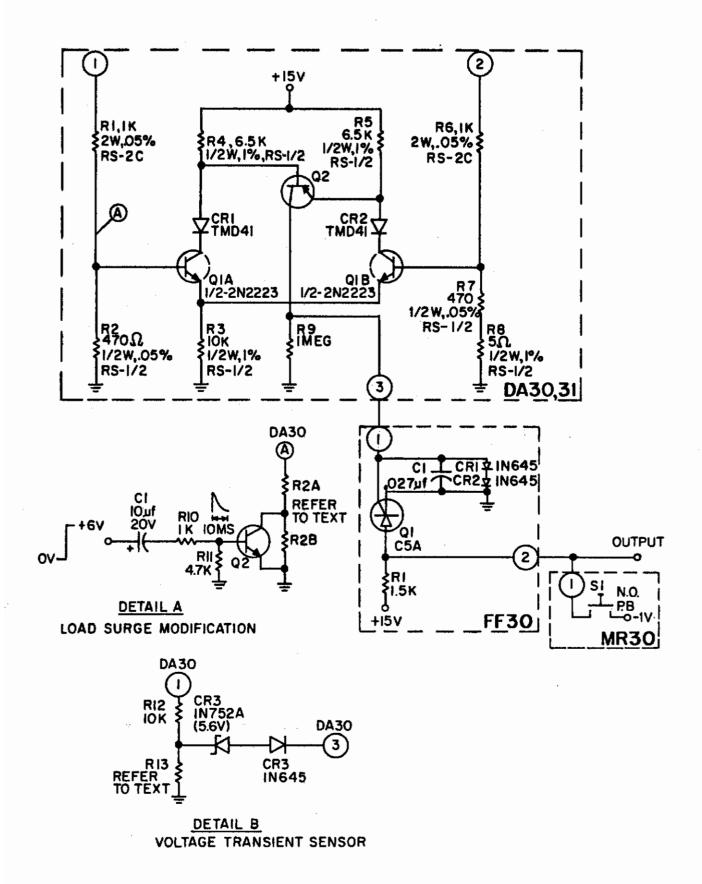

| 19         | DC Overload Circuits                                       | 72  |  |

| 20         | Delay Gate Multivibrator                                   | 75  |  |

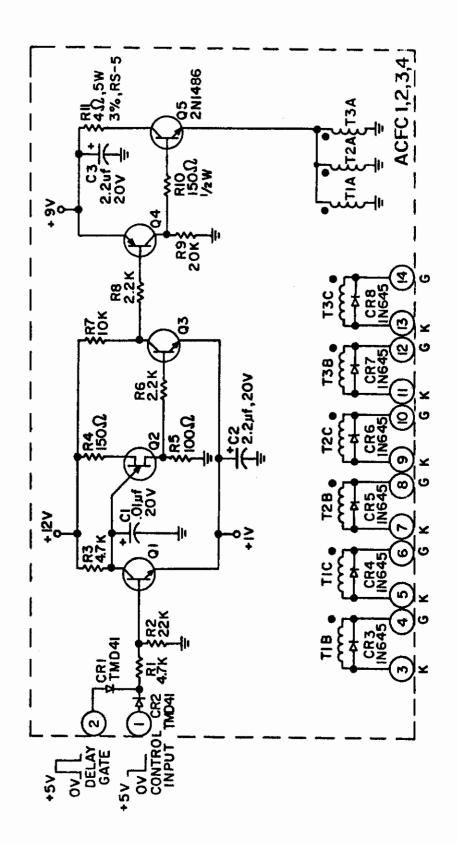

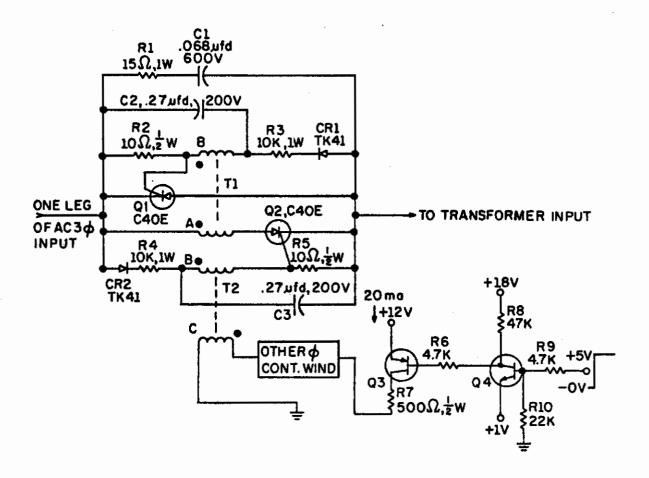

| 21         | AC Switch Firing Circuit                                   | 76  |  |

| 22         | AC Overload Circuits                                       | 77  |  |

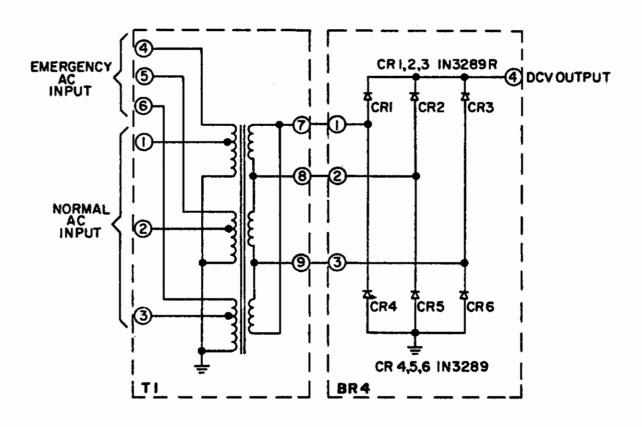

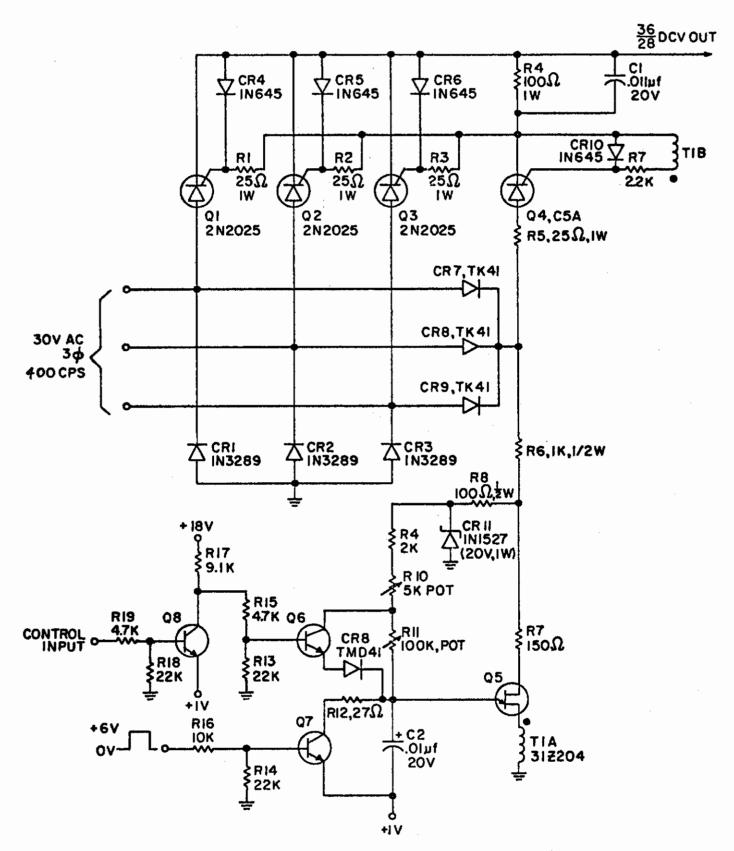

| 23         | Transformer-Rectifier                                      | 79  |  |

| 24         | Abstract Logic for Control Circuits                        |     |  |

|            | of the Anti-ice System                                     | 85  |  |

| 25         | Abstract Logic For Power Circuits of the Anti-ice System   | 88  |  |

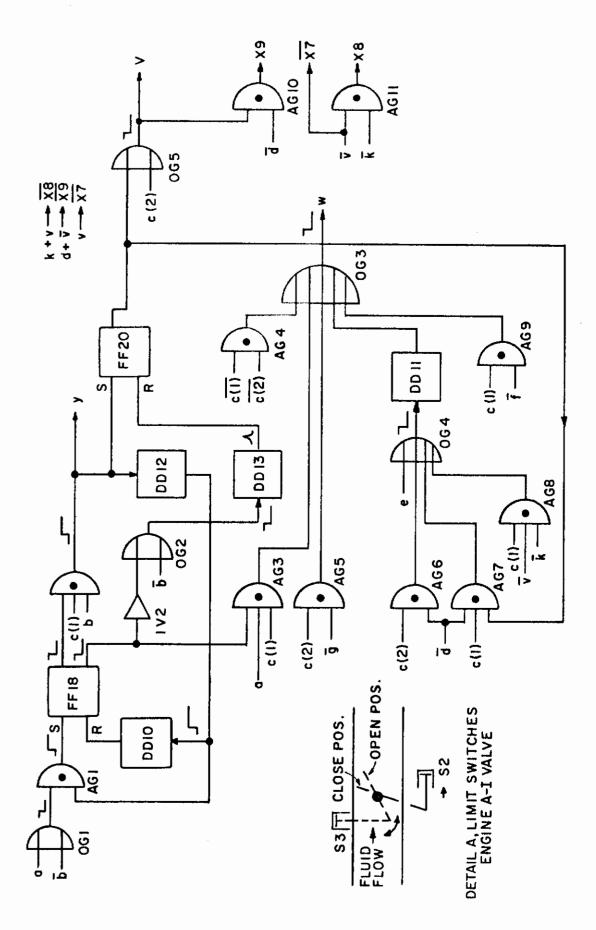

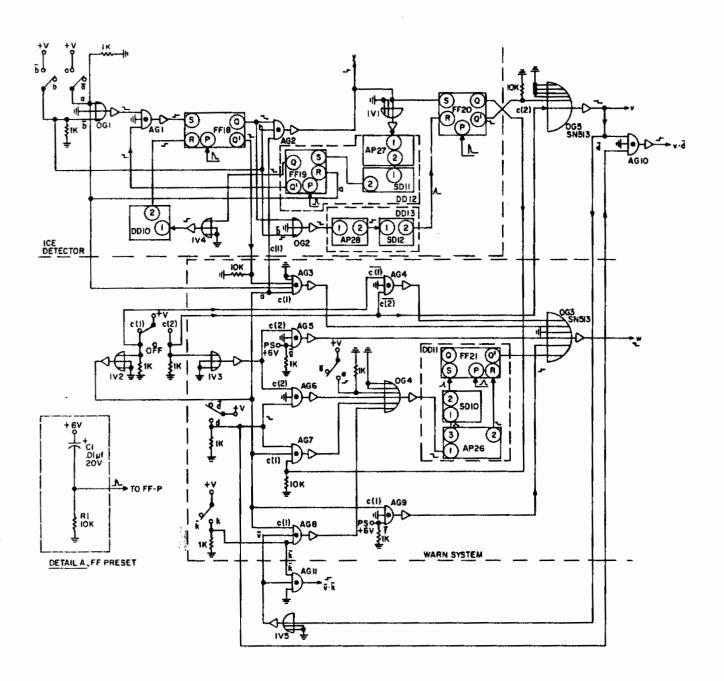

| 26         | Detailed Logic for Control Circuits of the Anti-ice System | 90  |  |

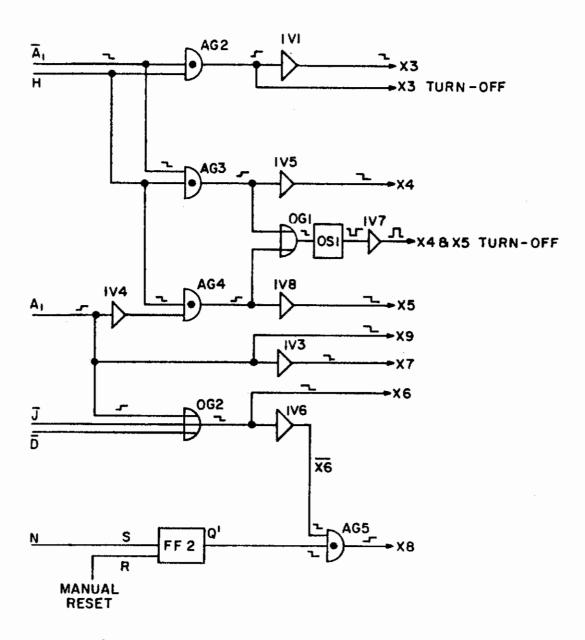

| 27         | Detailed Logic for Power Circuits of the Anti-ice System   | 93  |  |

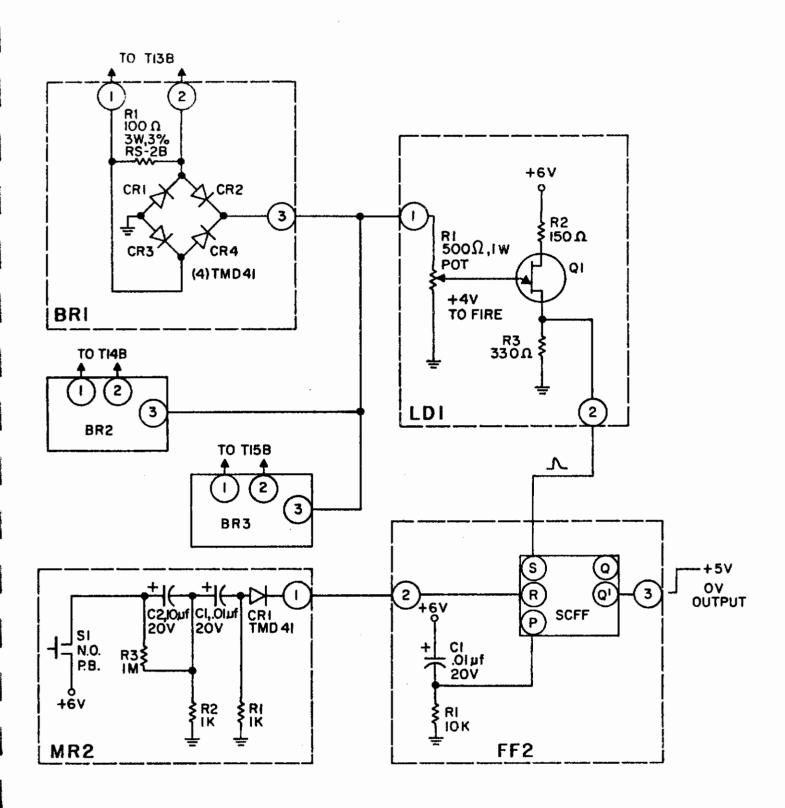

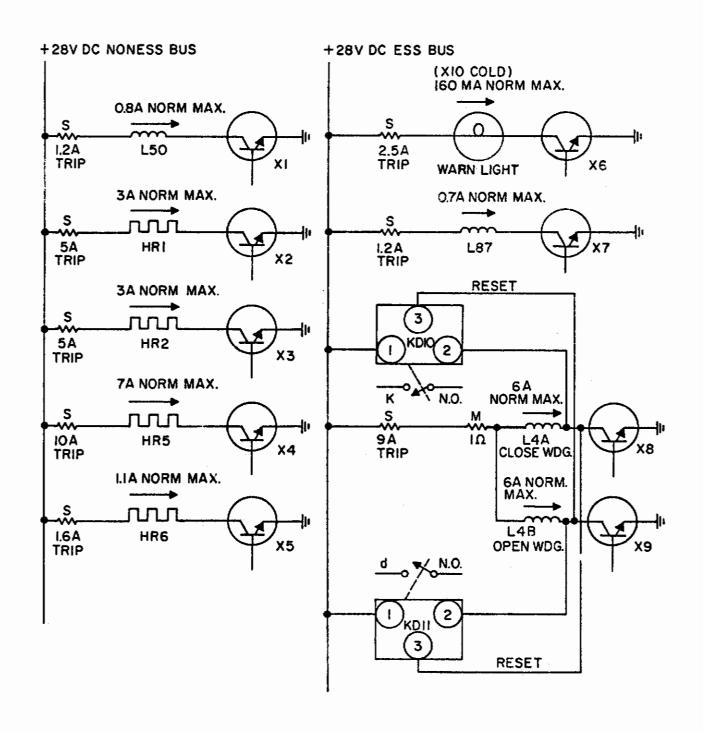

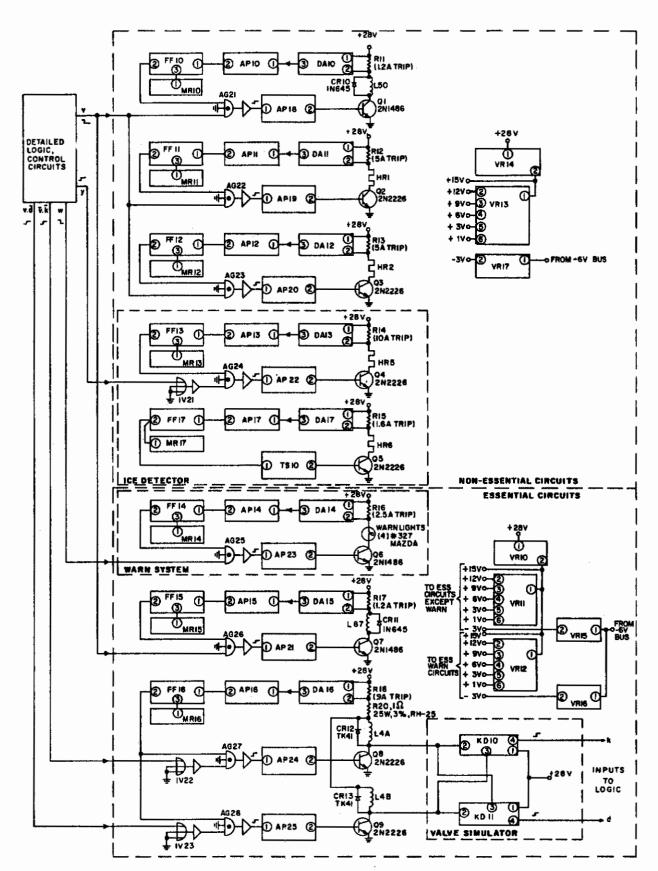

| 28         | Block Diagram of the Anti-ice System                       | 94  |  |

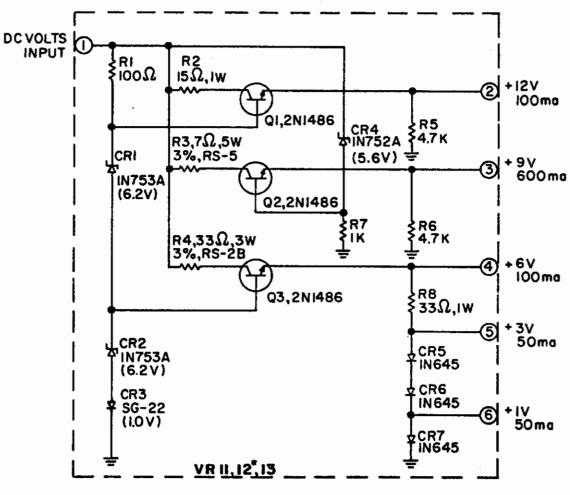

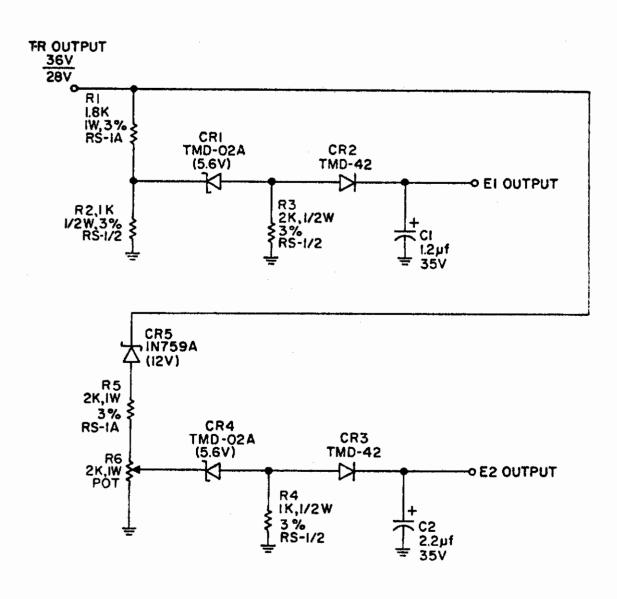

| 29         | Voltage Regulators (VRII, 12, 13)                          | 96  |  |

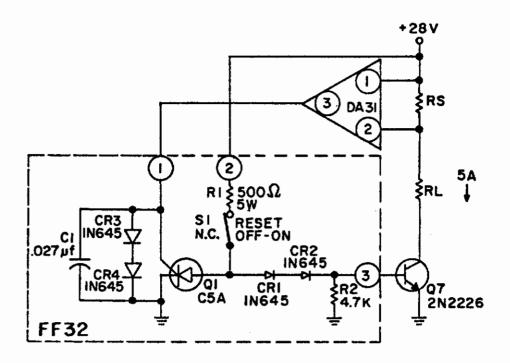

| 30         | Anti-ice Overload Flip-Flop and Manual                     | , , |  |

|            | Reset Circuit                                              | 99  |  |

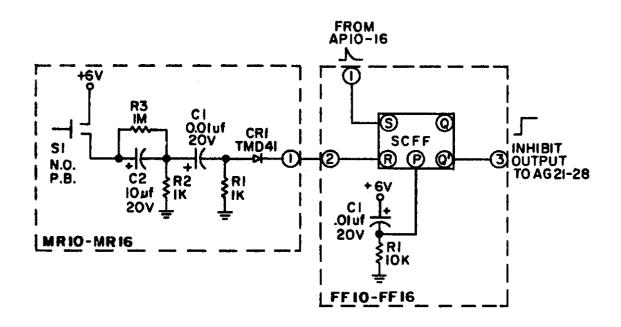

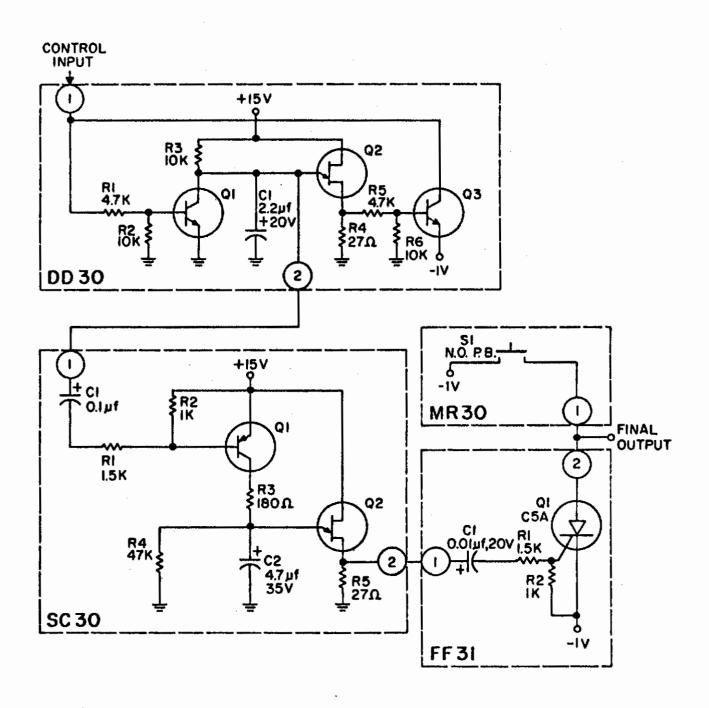

| 31         | Four Second Delay and Reset Delay Circuits                 | 100 |  |

| 32         | Eighteen and Sixty Second Delay Circuits                   | 101 |  |

| Figure No.                       | Title                                        |     |  |

|----------------------------------|----------------------------------------------|-----|--|

| 33                               | Temperature Sensor with Overload             |     |  |

|                                  | Flip-Flop and Reset Circuits                 | 103 |  |

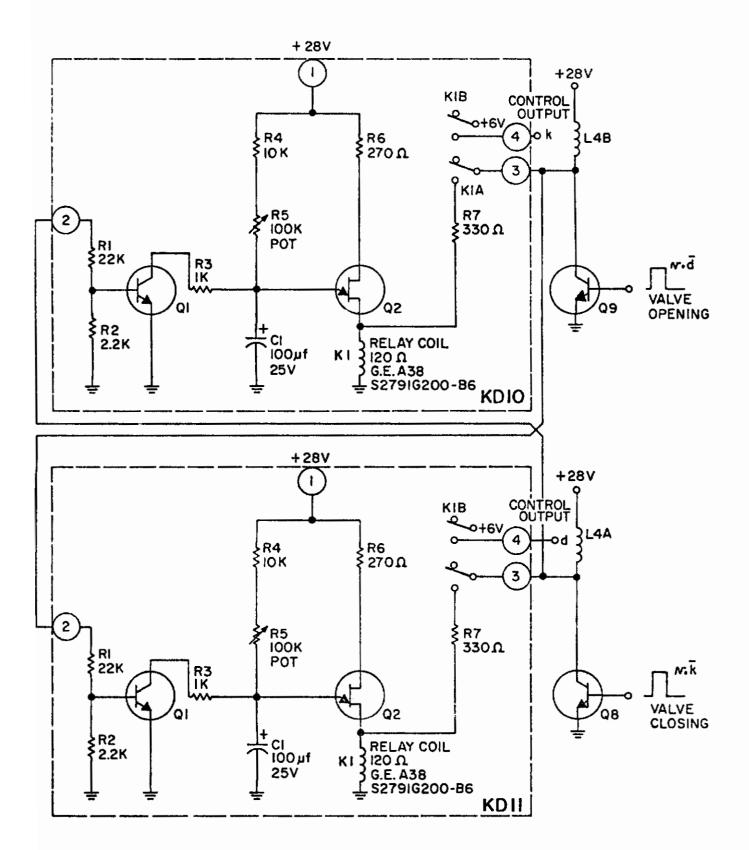

| 34                               | Simulation of Motor-driven Valve Operation   | 104 |  |

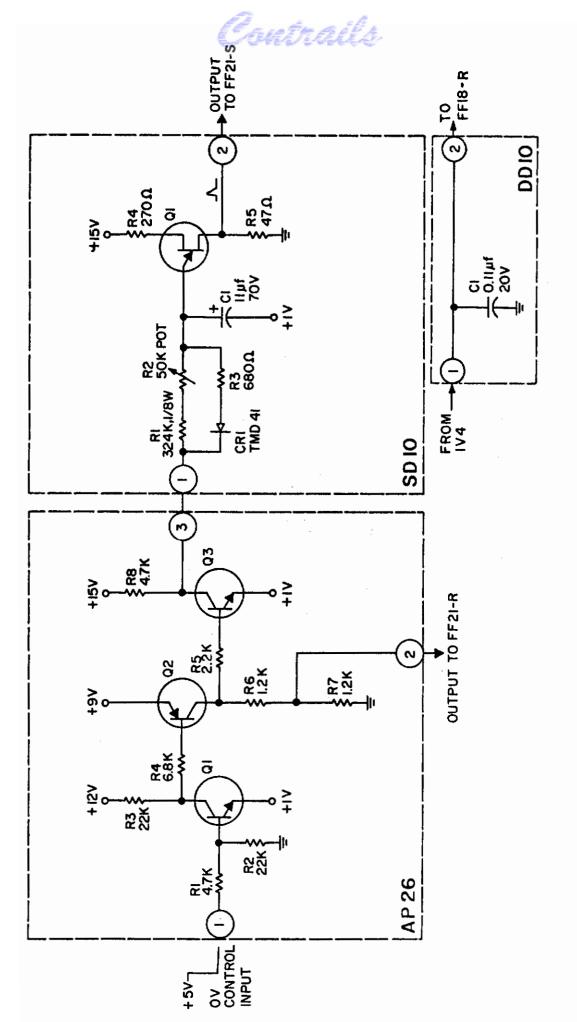

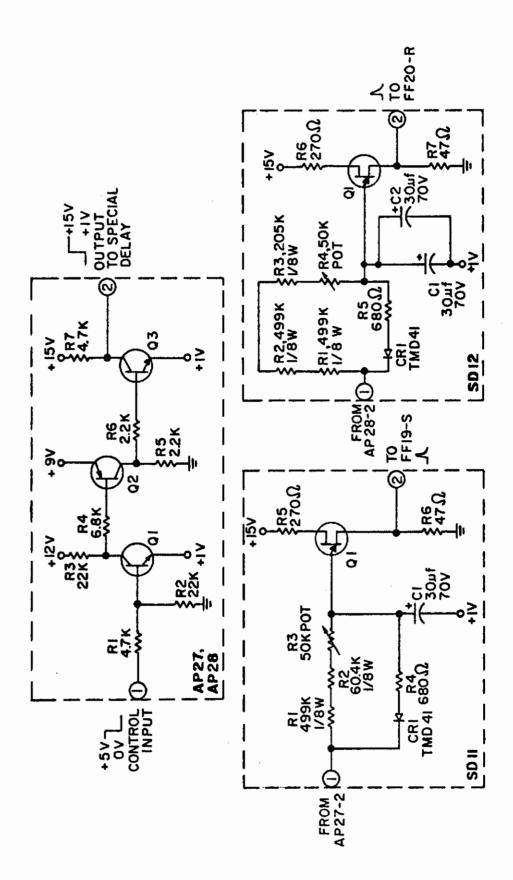

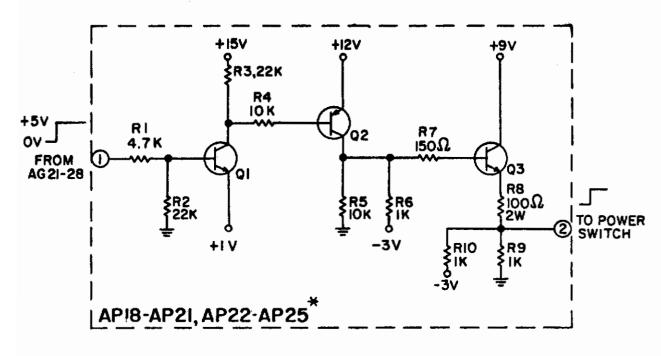

| 35                               | Power Switch Driving Amplifier               | 106 |  |

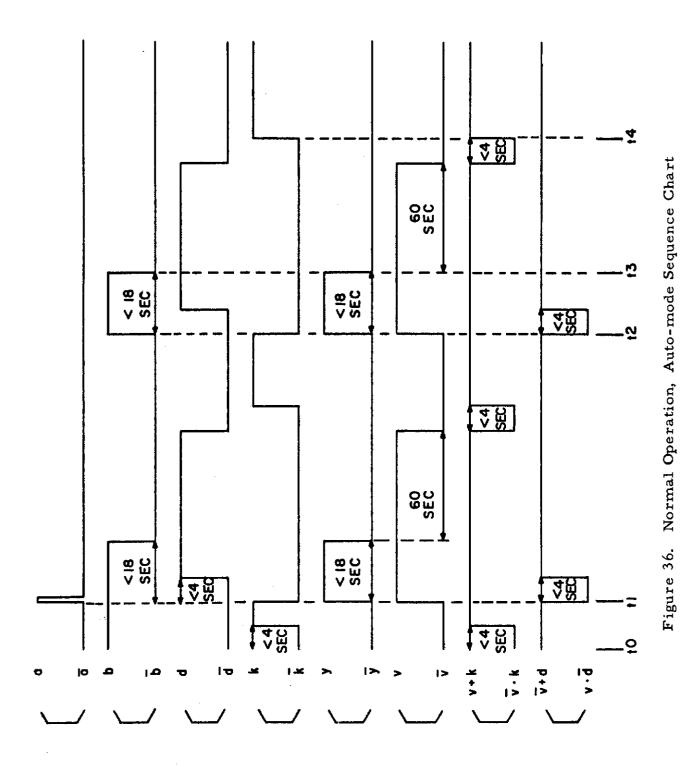

| 36                               | Normal Operation, Auto-mode Sequence Chart   | 110 |  |

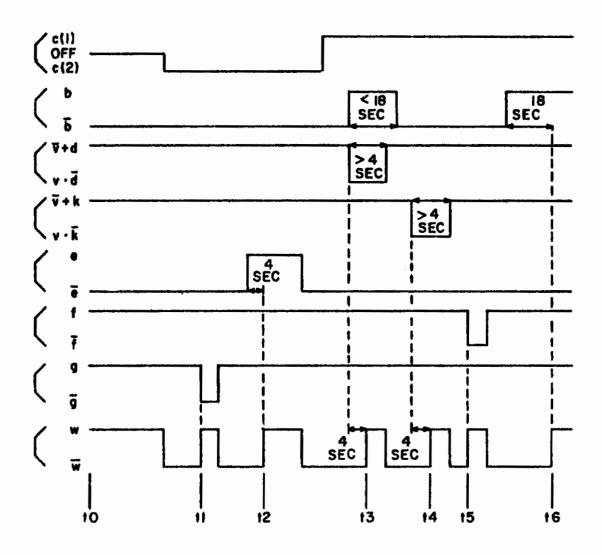

| 37                               | Warning Light Operation Sequence Chart       | 111 |  |

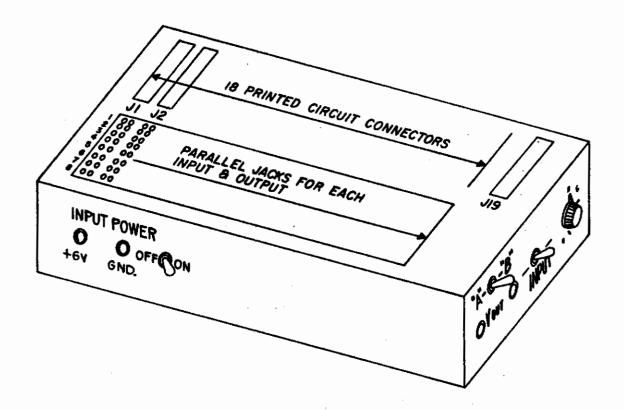

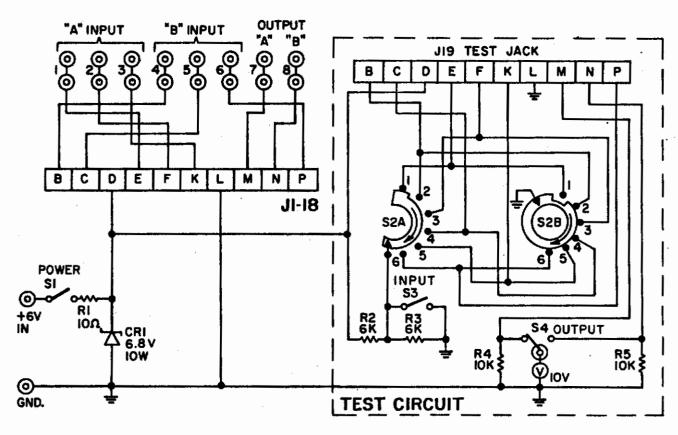

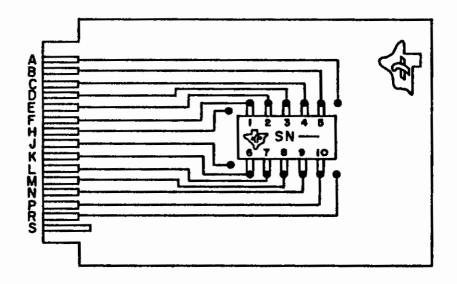

| 38                               | Solid Circuit Mounting Chassis               | 132 |  |

| 39                               | Solid Circuit Breadboard Mounting Board      |     |  |

|                                  | and Input Simulator                          | 133 |  |

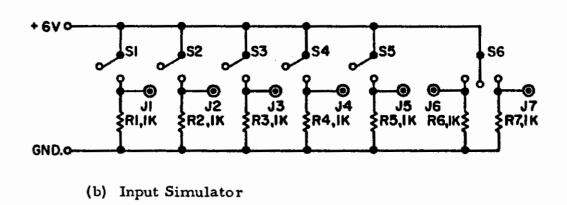

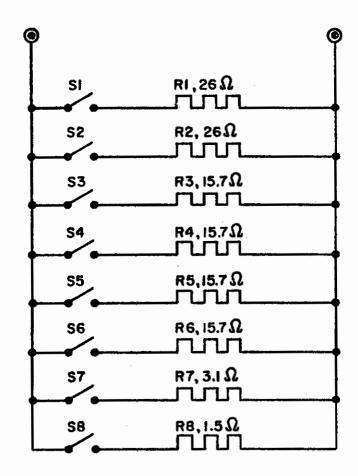

| 40                               | DC Simulated Load                            | 134 |  |

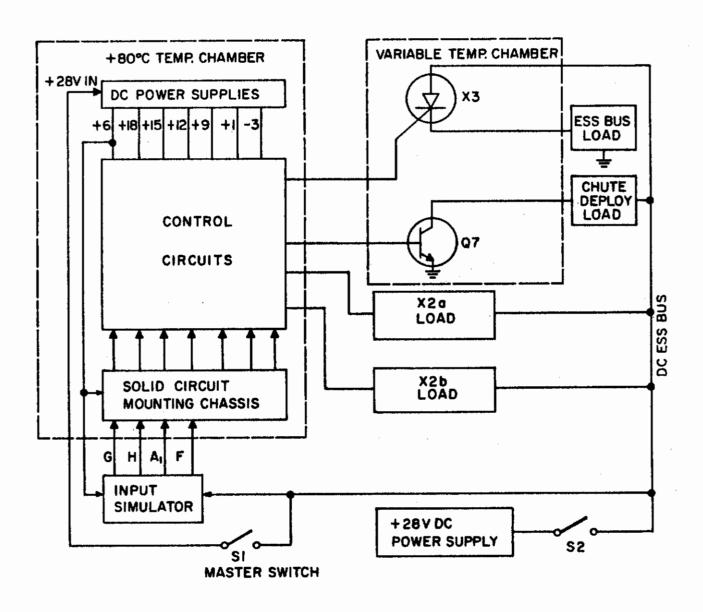

| 41                               | Test Set-up for DC Control Section           |     |  |

|                                  | High Temperature Run                         | 135 |  |

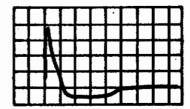

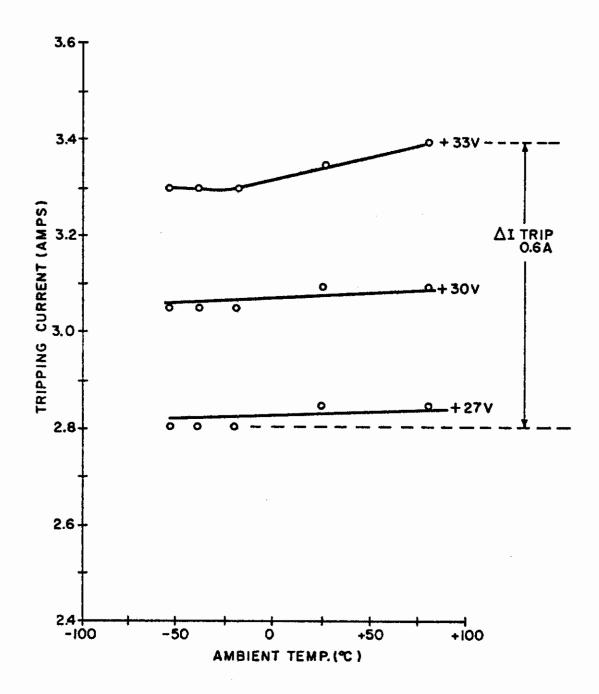

| 42                               | Modified DC Overload Circuit Performance     | 145 |  |

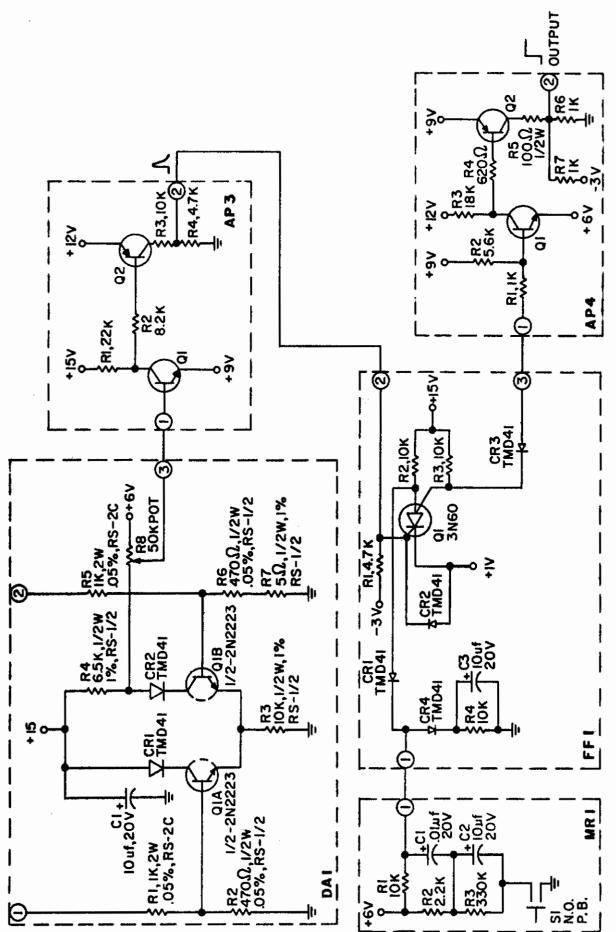

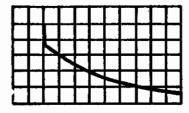

| 43                               | Differential Amplifier Performance           | 147 |  |

| 44                               | X3 Turn-On Waveforms                         | 154 |  |

| 45                               | X3 Turn-Off Waveforms                        | 155 |  |

| 46                               | AC Switch Waveforms                          | 161 |  |

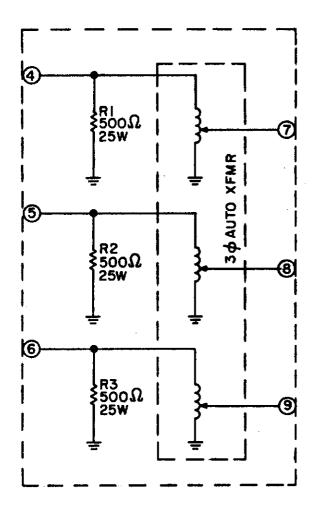

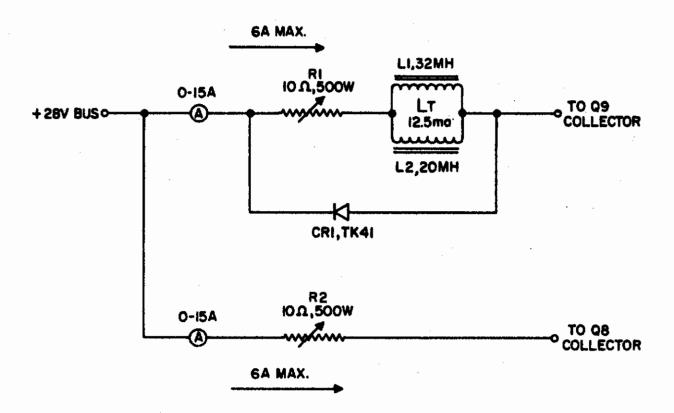

| 47                               | Simulation of TR Transformer, Tl             | 163 |  |

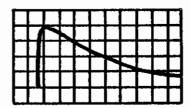

| 48                               | AC Overload Circuit Performance              | 165 |  |

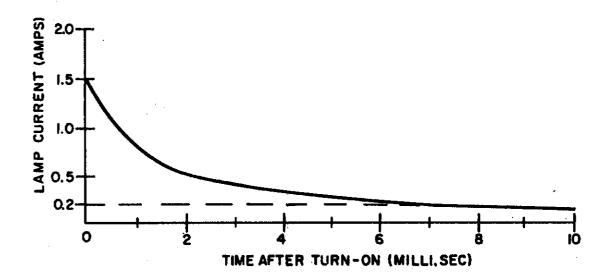

| 49                               | Lamp Current Surge at Turn-On                |     |  |

| 50                               | Warning Light Overload Circuit Performance   |     |  |

| 51                               | Simulation of Motor-driven Valve Load        |     |  |

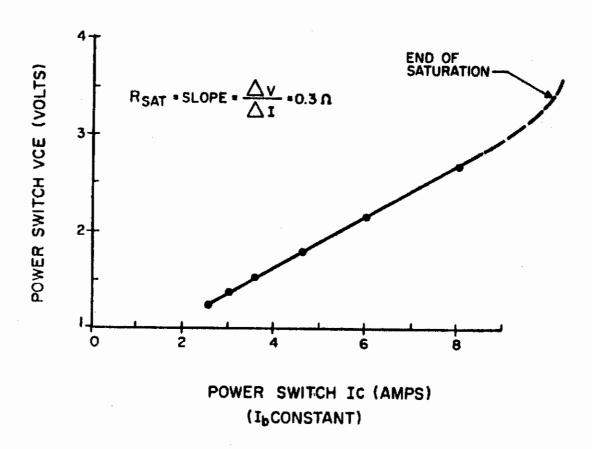

| 52                               | Determining Power Switch Saturation          |     |  |

| Resistance Variation of TS10-RT1 |                                              |     |  |

|                                  | with Temperature                             | 179 |  |

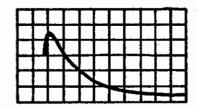

| 5 <b>4</b>                       | Case Heater Overload Circuit Performance     | 180 |  |

| 55                               | Phase Controlled, Full-Wave Bridge Rectifier | 183 |  |

| 56                               | TR Detection Circuit                         | 185 |  |

| 57                               | Original AC Switch and Firing Circuit        | 186 |  |

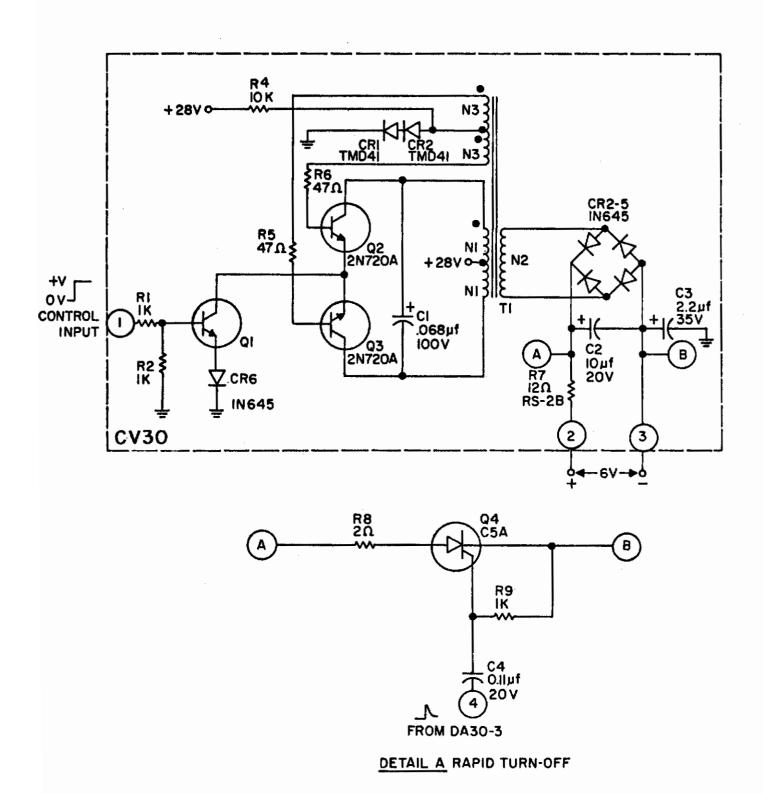

| 58                               | DC to DC Power Converter                     | 188 |  |

| 59                               | Emitter-Follower Power Switch with           |     |  |

|                                  | Cycling Overload System                      | 191 |  |

| 60                               | Improved DC Overload Detector and Flip-Flop  | 192 |  |

| 61                               | Improved DC Overload Circuit Performance     | 194 |  |

| 62                               | Simplified Chute Deploy Overload Circuit     | 195 |  |

| 63                               | Cycling Overload Circuits                    | 197 |  |

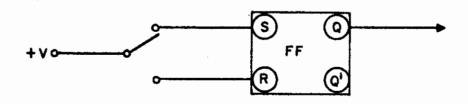

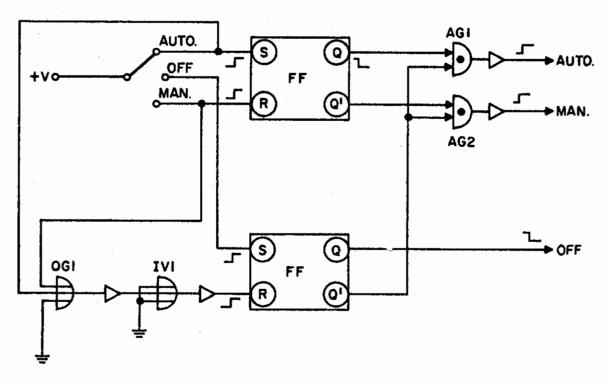

| I-1                              | Circuits to Eliminate Problems of            |     |  |

|                                  | Input Switch Contact Bounce                  | 219 |  |

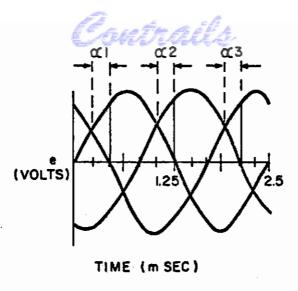

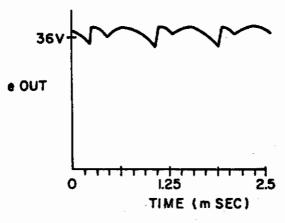

| I-2                              | Waveforms of the Phase-Controlled Bridge     | 236 |  |

## LIST OF TABLES

| 1         Summary of DC Power System         7           2         Equilibrium Temperatures Due to Solar Radiation         41           3         DC Flip-Flop Truth Table         47           4         Transistor Minimum Gain (hFE) Figures         49           5         Logical Definitions and Conditions for the DC Power Systems         55           6         Current Requirements for DC Power System in MA.         63           7         VR1, VR2, VR3, VR4, VR5 Thermal Conditions         65           8         Notes Applicable to the DC Overload Circuit         73           9         DC Power System Power Switch Thermal         Conditions         81           10         Conditions and Definitions for Control Logic         86           11         Notes - Abstract Logic, Power Circuits         89           12         Power Requirements for the Anti-ice System         97           13         Regulator Thermal Conditions         98           14         Amplifier Power Requirements (AP18-25)         107           15         Anti-ice Power Switch Thermal Conditions         108           16         DC Regulator (VR1, VR2) Circuit Voltages         137           17         DC Regulator (VR1, VR2) Performance Data         141           18B |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Equilibrium Temperatures Due to Solar Radiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4 Transistor Minimum Gain (h <sub>FE</sub> ) Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5         Logical Definitions and Conditions for the DC Power Systems         55           6         Current Requirements for DC Power System in MA         63           7         VR1, VR2, VR3, VR4, VR5 Thermal Conditions         65           8         Notes Applicable to the DC Overload Circuit         73           9         DC Power System Power Switch Thermal Conditions         81           10         Conditions and Definitions for Control Logic         86           11         Notes - Abstract Logic, Power Circuits         89           12         Power Requirements for the Anti-ice System         97           13         Regulator Thermal Conditions         98           14         Amplifier Power Requirements (AP18-25)         107           15         Anti-ice Power Switch Thermal Conditions         108           16         DC Regulator (VR1, VR2) Circuit Voltages         137           17         DC Regulator (VR1, VR2) Performance Data         138           18A         Negative Power Supply (PS2) Performance Data         141           18B         Negative Regulator (VR3) Performance Data         141           19         Chute Deploy Overload Circuit Voltages         142                                                          |

| 5         Logical Definitions and Conditions for the DC Power Systems         55           6         Current Requirements for DC Power System in MA         63           7         VR1, VR2, VR3, VR4, VR5 Thermal Conditions         65           8         Notes Applicable to the DC Overload Circuit         73           9         DC Power System Power Switch Thermal Conditions         81           10         Conditions and Definitions for Control Logic         86           11         Notes - Abstract Logic, Power Circuits         89           12         Power Requirements for the Anti-ice System         97           13         Regulator Thermal Conditions         98           14         Amplifier Power Requirements (AP18-25)         107           15         Anti-ice Power Switch Thermal Conditions         108           16         DC Regulator (VR1, VR2) Circuit Voltages         137           17         DC Regulator (VR1, VR2) Performance Data         138           18A         Negative Power Supply (PS2) Performance Data         141           18B         Negative Regulator (VR3) Performance Data         141           19         Chute Deploy Overload Circuit Voltages         142                                                          |

| 6 Current Requirements for DC Power System in MA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| System in MA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7 VR1, VR2, VR3, VR4, VR5 Thermal Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8 Notes Applicable to the DC Overload Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DC Power System Power Switch Thermal Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Conditions and Definitions for Control Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Notes - Abstract Logic, Power Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Power Requirements for the Anti-ice System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Regulator Thermal Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Amplifier Power Requirements (AP18-25)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Anti-ice Power Switch Thermal Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DC Regulator (VR1, VR2) Circuit Voltages at No Load and +27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| at No Load and +27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DC Regulator (VR1, VR2) Performance Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Negative Power Supply (PS2) Performance Data 141 Negative Regulator (VR3) Performance Data 141 Chute Deploy Overload Circuit Voltages at 27°C 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Negative Regulator (VR3) Performance Data 141  Chute Deploy Overload Circuit Voltages at 27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19 Chute Deploy Overload Circuit Voltages at 27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| at 27°C 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21A Modified Chute Deploy Overload Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Performance Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21B Saturation Voltages for the Q7 Power Switch while                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Conducting with 55 Milliamperes Base Drive 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

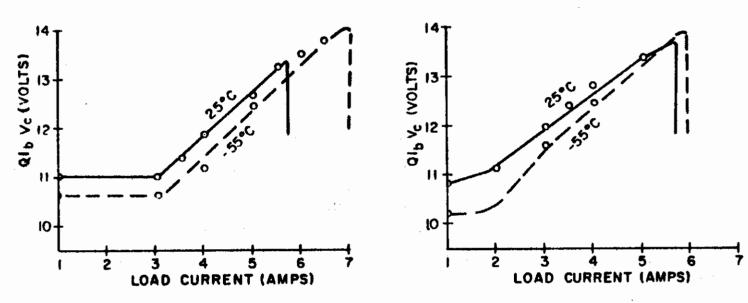

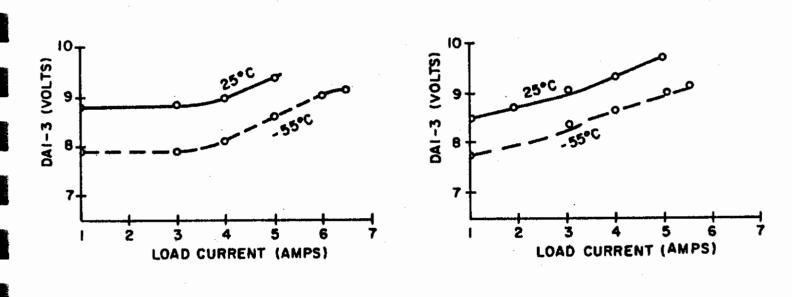

| Differential Amplifier (DAI) Performance Data 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| External Power Interlock (X2a and AP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Circuit Voltages at +27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24 Generator Power Interlock (X2b and AP2) Circuit Voltages at +27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25A Performance Data for X2a and X2b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| when Conducting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 25B Performance Data for X2a and X2b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| when Not Conducting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 26 Firing Circuit (FC1) Voltages at +27°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table No. | Title                                            |     |

|-----------|--------------------------------------------------|-----|

| 27        | X3 Turn-Off Circuit (TO1) Voltages at +27°C      | 153 |

| 28A       | X3, FCl, and TOl Performance Data                | 156 |

| 28B       | Saturation Voltages for the X3 Power Switch      |     |

|           | while Conducting 40 amperes                      | 156 |

| 29        | Voltage Sensor VS1, VS2 Performance Data         | 158 |

| 30        | AC to DC Power Supply (PSI) Performance Data     | 159 |

| 31        | AC Firing Circuit Voltages at +25°C              | 160 |

| 32        | AC Overload Circuit Voltages at +25°C            | 162 |

| 33        | AC Overload Circuit Performance Data             | 164 |

| 34        | Delay Gate Multivibrator (OS1) Circuit           |     |

|           | Voltages at +25°C                                | 166 |

| 35        | X4 and X5 Firing Circuits (FC2, FC3)             |     |

|           | Voltages at +25°C                                | 166 |

| 36        | Time Delay Circuit Voltages at +25°C             | 169 |

| 37        | Time Delay Performance Data                      | 170 |

| 38        | Amplifier (AP21, AP23) Circuit Voltages at +25°C | 171 |

| 39        | Warning Light Overload Circuit Performance Data  | 174 |

| 40        | Performance Data for Motor-driven Valve Power    |     |

|           | Switch (Q8 or Q9) while Conducting               | 174 |

| 41        | Temperature Sensor (TS10) Circuit Voltages at    |     |

|           | +25°C                                            | 176 |

| 42        | Case Heater Overload Circuit Performance Data    | 178 |

| 43        | TR Detection Circuit Performance Data at +25°C   | 184 |

| 44        | DC to DC Converter Performance Data at +27°C     | 189 |

| 45        | Emitter-Follower Power Switch Performance        |     |

|           | Data at +25°C                                    | 189 |

| 46        | Improved DC Overload Circuit Performance Data    | 193 |

| T-1       | Truth Tables of Fundamental Operations           | 215 |

#### INTRODUCTION

An electrical power system can be regarded as consisting of an energy source, utilization devices, and the transmission link that connects them. Components in the transmission link must often serve a dual purpose in that they not only control electrical energy flow but also provide protection against overloads. Present-day transmission links in aircraft consist of switches, contractors, relays, and circuit breakers, all of which utilize mechanical motion. Thus, they exhibit failures due to pitting, misaligned contacts, and other causes common to electromechanical devices.

The advent of space vehicles has placed increased emphasis on reliability and long life, and therefore, transmission links of increased reliability and longer life are required. Thus, the goal of this program was to develop a highly reliable, efficient, and practical solid state transmission link having positive advantages over conventional electromechanical transmission links. Primary emphasis was on higher reliability and longer life, but improved performance and reduced size and weight were considered highly desirable.

The basic approach for achieving the optimum solid state system was to subject the entire transmission link to an overall functional analysis, and then redesign the logic system to make the most efficient use of solid state devices. Also, dual functions such as control and protection were combined into a single power handling device wherever possible. The equivalent solid state circuit contained all the original circuit operational functions plus the improved functions or characteristics made possible by solid state technology.

This program was divided into 2 phases. During the first phase, which was completed in October, 1962, 2 transmission links of the F-106B were redesigned as solid state systems. They had been selected only as representative examples of the functions and loads that transmission links must support in an advanced aerospace vehicle.

During the second phase, which was completed in July, 1963, the designed systems were tested and a design manual was prepared. The following paragraphs discuss the 8 separate tasks that were performed during the program. The first 5 comprised the first phase and the last 3 comprised the second phase.

The first task was to analyze the operating sequence and functions of the 2 transmission links of the F-106B that were under consideration. These were the following:

Manuscript released by the authors 30 July 1963 for publication as an ASD Technical Documentary Report.

- (1) Schematic Diagram Master Electrical, Surface & Engine Anti-Ice, nr. 8-69741, Rev. G, sheet 3 (presented in T.O. 1F-106A-2-10 as Figure 12-51, Surface and Engine Air Anti-Ice Schematic);

- (2) Schematic Diagram Master Electrical, DC Power, nr. 8-69770, Rev. B, sheet 5 (presented in T.O. 1F-106A-2-10 as Figure 12-90, DC Power Schematic, sheet 2 of 3).

The analysis had to provide sufficient data to make possible the logic and circuit design of solid state systems that would provide all the functions provided by the original electromechanical systems. The analysis of the schematics was divided into 3 parts: (1) description of operation; (2) definition of system bounds; and (3) system loads.

The second task was to evaluate the suitability of semiconductor devices for the anticipated logic and circuit requirements of the systems. The devices needed were divided into power switching devices and control circuit devices. Controlled rectifiers, power transistors, and conventional rectifiers were evaluated as power switching devices. Discrete devices and functional devices were evaluated as control circuit devices.

The third task was to determine the most reasonable temperature range for which to design the circuitry. The anticipated thermal environment was reviewed and the temperature ranges of present devices and circuitry was considered. It was decided to design for an operating temperature range of -55° C to +80° C and for a storage temperature range of -55° C to +125° C.

The fourth task was to provide the logic design and circuit design. It was based on the overall functional analysis made initially and was devised to make the most efficient use of solid state devices. For example, the dual functions of control and protection were combined into a single power switching device. The solid state systems provided all the functions of the original electromechanical systems plus the improved characteristics made possible by solid state techniques.

The fifth task was to prepare a general specification for the solid state system that had been designed. This consisted basically of 2 sections; (1) the requirements; and (2) the experimental evaluation procedure. Also a preliminary evaluation was made of the extent of advantage of the solid state systems over conventional electromechanical systems.

The sixth task was to test the solid state systems. The systems were divided into 3 sections and the tests were conducted separately for each section. The results of these tests were good. All circuitry operated properly under the specified conditions.

The seventh task was to design and test alternate circuits. The evaluation of the designed systems revealed that certain simple design modifications could be effected that would considerably improve the solid state systems. Therefore, alternate circuits were designed to achieve these improvements.

The eighth task was to prepare a design manual that set forth the design criteria, problem areas, and installation considerations necessary to apply solid state transmission links in aerospace vehicles. This design manual is presented in Appendix I.