AFFDL-TR-66-81

### **SOLID-STATE DISPLAY DEVICES**

GLENN VAN WINKLE MARK DEBONO LEAR SIEGLER, INC.

TECHNICAL REPORT AFFDL-TR-66-81

AUGUST 1966

Distribution of this document is unlimited

AIR FORCE FLIGHT DYNAMICS LABORATORY

RESEARCH AND TECHNOLOGY DIVISION

AIR FORCE SYSTEMS COMMAND

WRIGHT-PATTERSON AIR FORCE BASE, OHIO 45433

This program was initiated by the Control Systems Research Branch, Flight Control Division, AF Flight Dynamics Laboratory, under Task 619009, ''Advanced Display Generation Techniques'' of Project 6190 under the direction of Mr. J.H. Kearns, III and Mr. E. Warren. Mr. R.W. Schwartz served as the Task Scientist and Contract Monitor until he was succeeded by Captain C.J. Peterson in September 1963.

The studies presented began in May 1963 and were concluded in June 1965 under Contract AF33(657)-11554 with the Solid-State Display Department of the Instrument Division of Lear Siegler, Inc. Although the studies were a group effect, the chief contributors were Mr. Glenn L. Van Winkle, Section Head, and Mr. Mark De Bono, the Project Engineer.

Even though difficulties were encountered in the large scale use of photoconductor materials for the control of real time electroluminescent displays, the results of research performed under this program are considered an important step in the development of practical solid state displays. The most significant development to be reported is the application of new display filtering techniques capable of permitting legible use of low emission displays in high light ambient surroundings.

This report has been reviewed and is approved.

Koren A. Anderson LOREN A. ANDERSON, Major, USAF

Chief, Control Systems Research Br.

Flight Control Division

The manuscript was released by the authors in June 1966 for publication as an RTD technical documentary report.

### ABSTRACT

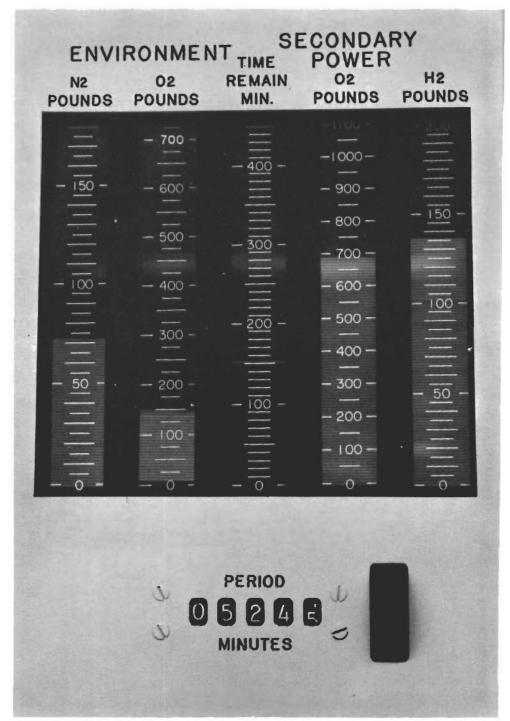

The result of this program was the development of a solid-state display device utilizing binary input information. An extension of previous contract work, the program produced the application of thin film photoconductive elements, with as many as 128 individual switching elements on a single substrate. The photoconductor switches are driven with electroluminescent lamps. The readout is made up of five columns of segmented electroluminescent lamps with a resolution of 32 lines per inch. Four of the columns are of the thermometer type while the fifth is a single line which moves as a time reference.

| Section |                                         | Page |

|---------|-----------------------------------------|------|

| 1       | INTRODUCTION                            | 1    |

|         | Purpose                                 | 1    |

|         | Background                              | 2    |

|         | Piezoelectric Control                   | 2    |

|         | Dinepcel                                | 2    |

|         | EL-PC-EL                                | 3    |

| 2       | EL-PC MATRIX                            | 4    |

|         | Logic                                   | 4    |

|         | Three-Bit Translator                    | 4    |

|         | Address Circuitry                       | 7    |

|         | Hold Circuitry                          | 7    |

|         | PC Substrates: Three-Bit Translator     | 9    |

|         | Display Lamp                            | 14   |

|         | Electronics System                      | 14   |

|         | Shaft Angle Encoder and Driver          | 14   |

|         | SCR Switches                            | 19   |

| 3       | EL-PC SYSTEM ANALYSIS                   | 22   |

|         | EL Lamps                                | 22   |

|         | Photoconductors                         | 23   |

|         | The Problem                             | 25   |

|         | Transient Analysis                      | 26   |

|         | Final Configuration Diode Transistor    | 29   |

|         | EL-PC Logic                             | 20   |

| 4       | CONVERSION LOGIC                        | 37   |

|         | Storage Registers                       | 37   |

|         | Three-Bit Binary-to-Decimal Thermometer | 37   |

# TABLE OF CONTENTS (cont)

| Section |                                    | Page |

|---------|------------------------------------|------|

|         | Four-Bit Line-to-Thermometer and   | 39   |

|         | Time Delay                         | 39   |

|         | SCR Driver Circuits                | 41   |

|         | SCR Module Description             | 44   |

|         | EL-PC Switching                    | 44   |

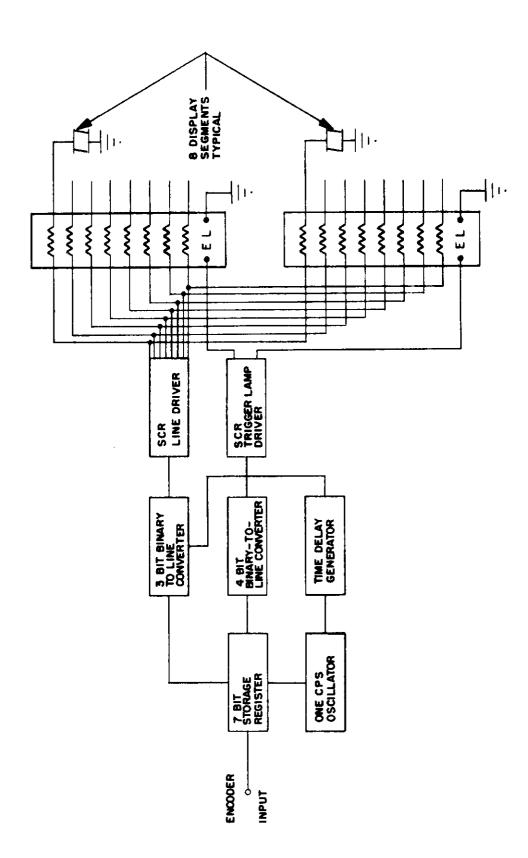

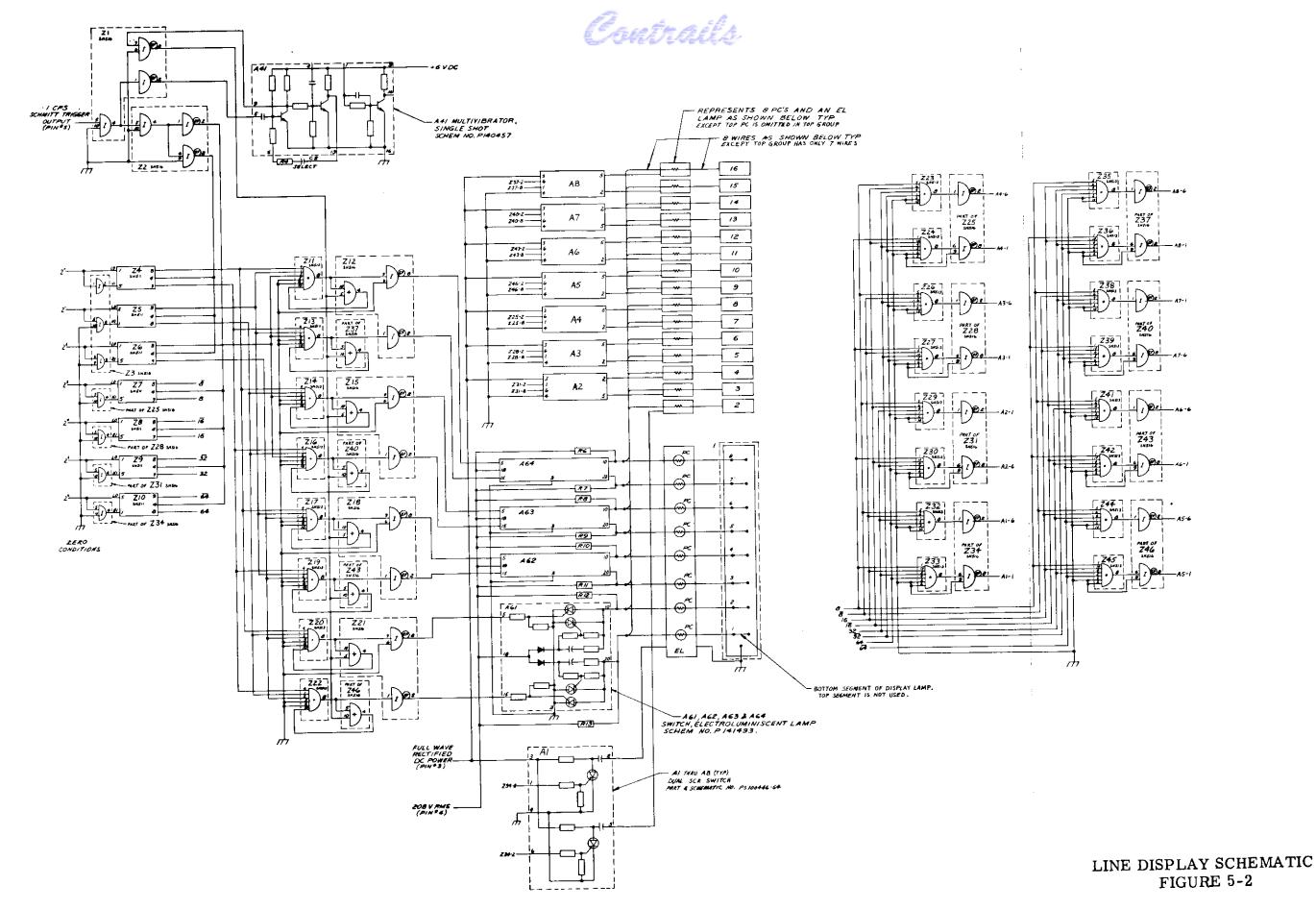

| 5       | LINE DISPLAY LOGIC SYSTEM          | 47   |

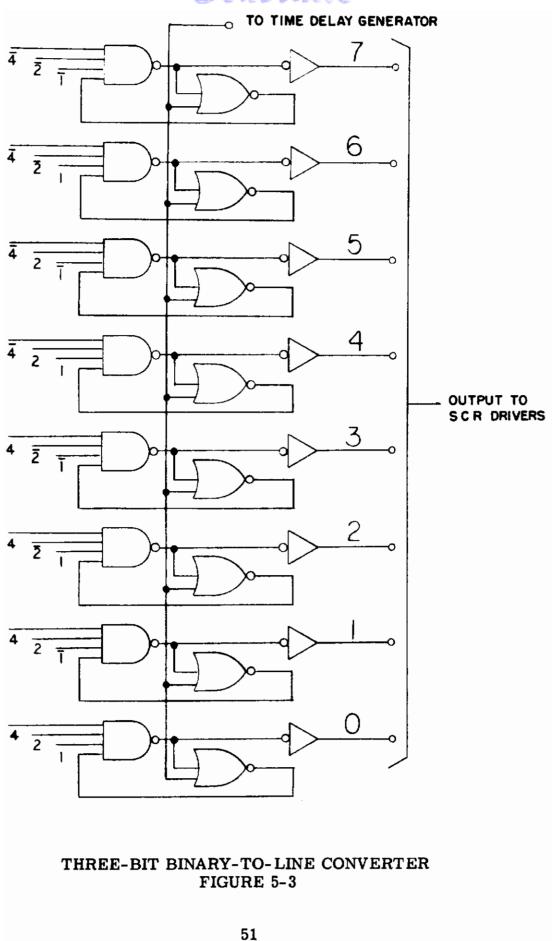

|         | Three-Bit Binary-to-Line Converter | 47   |

|         | Storage Registers                  | 47   |

|         | Four-Bit Binary-to-Line Converter  | 52   |

|         | SCR Driver Circuits                | 52   |

|         | Time Delay                         | 52   |

|         | EL-PC Switching                    | 52   |

| 6       | POWER SUPPLY                       | 54   |

| 7       | PACKAGING                          | 58   |

| 8       | READABILITY OF THE DISPLAY         | 63   |

| 9       | OPERATION OF THE DISPLAY           | 65   |

|         | Response Time                      | 65   |

|         | Time Delays                        | 65   |

|         | Temperature and Power Requirements | 65   |

| Figure | Title                                                              | Page       |

|--------|--------------------------------------------------------------------|------------|

| 1-1    | Environmental and Secondary Power Display                          | ix         |

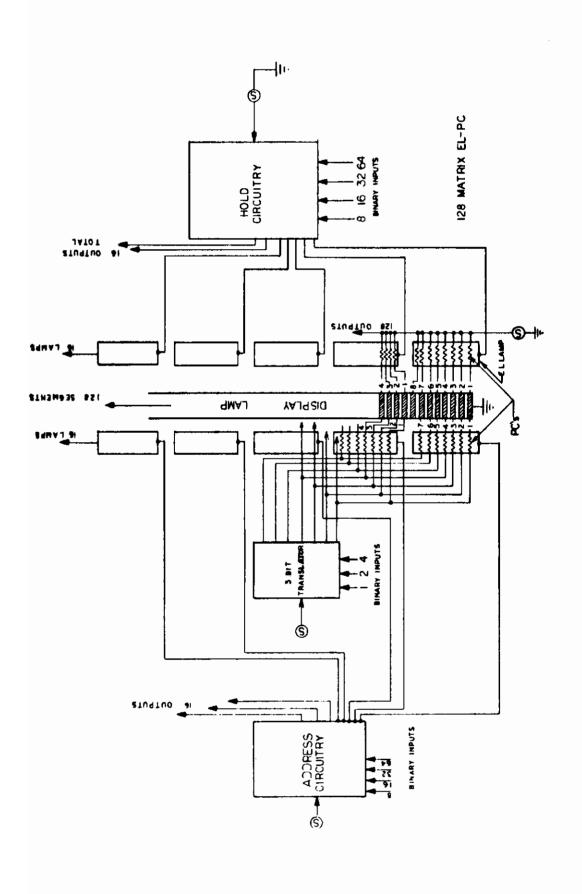

| 2-1    | EL-PC Matrix Block Diagram                                         | 5          |

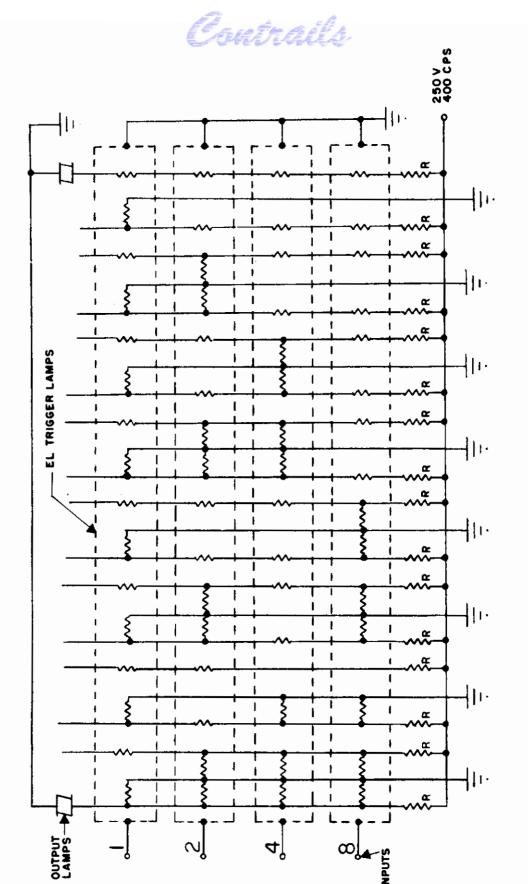

| 2-2    | Three-Bit Translator Schematic                                     | 6          |

| 2-3    | Address Select Circuit                                             | 8          |

| 2-4    | Three-Bit Translator Electrode Pattern                             | 10         |

| 2-5    | Hold Select Electrode Pattern                                      | 11         |

| 2-6    | Address Select Electrode Pattern                                   | 12         |

| 2-7    | EL Trigger Lamp                                                    | 13         |

| 2-8    | Address Circuit Electrode Pattern                                  | 15         |

| 2-9    | Hold Circuit Electrode Pattern                                     | 16         |

| 2-10   | Trigger Lamp Layout for the Address and Hold Circuits              | 17         |

| 2-11   | Scale Marking for the Five Channels                                | 18         |

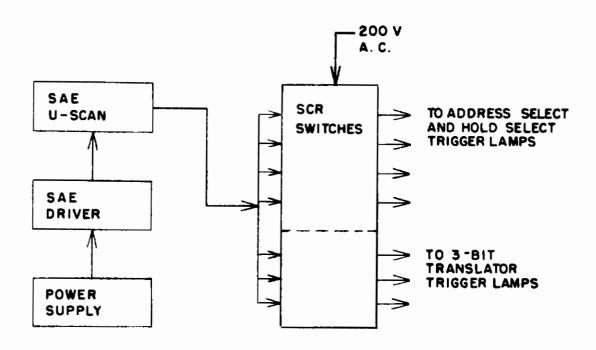

| 2-12   | Original Electronic System Block Diagram                           | 19         |

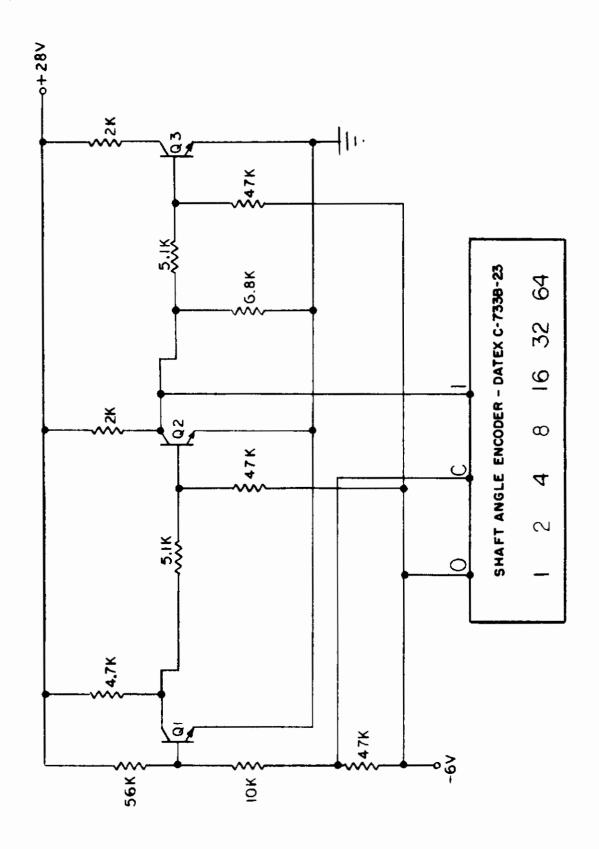

| 2-13   | Encoder Driver Circuit Schematic Diagram                           | 20         |

| 3-1    | Applied Voltage Vs. EL Brightness Curves                           | 23         |

| 3-2    | Typical Time Response Curves for                                   | 24         |

| 3-3    | Series EL-PC Switching Circuit                                     | 26         |

| 3-4    | Photoconductor Response for a Single Gap                           | <b>2</b> 8 |

| 3-5    | Thermometer Display Block Diagram                                  | 30         |

| 3-6    | Thermometer Display Schematic                                      | 31         |

| 4-1    | Three-Bit Storage Register                                         | 37         |

| 4-2    | Seven-Bit Storage Register                                         | <b>3</b> 8 |

| 4-3    | Three-Bit Binary-to-Thermometer Converter                          | 40         |

| 4-4    | Hold Logic Circuit                                                 | 41         |

| 4-5    | Four-Bit Binary-to-Line Converter                                  | 42         |

| 4-6    | Time Delay to Delay Lamp Turn ON                                   | 43         |

| 4-7    | Time Delay to Delay Lamp Turn ON Time Delay to Delay Lamp Turn OFF | 43         |

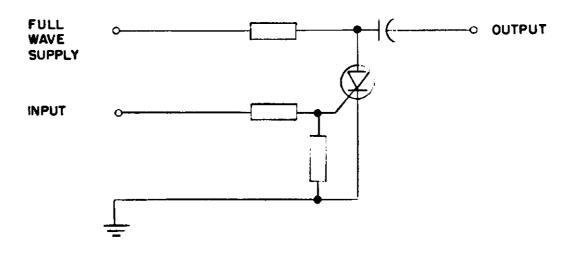

| 4-8    | SCR Full Wave Supply Driver Circuit                                | 45         |

| 4-9    | SCR AC Supply Driver Circuit                                       | 45         |

| 4-10   | System Switching Logic with EL-PC                                  | 46         |

## LIST OF ILLUSTRATIONS (cont)

| Figure | Title                                        | Page |

|--------|----------------------------------------------|------|

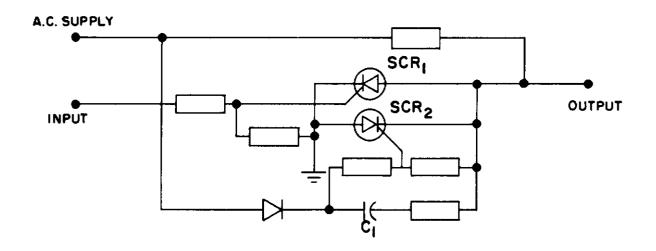

| 5-1    | Line Display Block Diagram                   | 48   |

| 5-2    | Line Display Schematic                       | 49   |

| 5-3    | Three-Bit Binary-to-Line Converter           | 51   |

| 5-4    | EL-PC Switching Logic                        | 53   |

| 6-1    | One CPS Oscillator and Schmitt Trigger       | 55   |

| 6-2    | Encoder Driver Circuit                       | 56   |

| 6-3    | Full Wave Rectified Supply                   | 57   |

| 7-1    | Completely Assembled Single Channel          | 59   |

| 7-2    | Opened-Up Single Channel                     | 60   |

| 7-3    | Right Angle Connection - Display Lamp Matrix | 62   |

### LEGEND

|                | RESISTOR       |

|----------------|----------------|

| <b>~~~</b>     | PHOTOCONDUCTOR |

| <u></u>        | NAND GATE      |

|                | NOR GATE       |

| $\diamondsuit$ | INVERTER       |

|                | EL LAMP        |

ENVIRONMENTAL AND SECONDARY POWER DISPLAY FIGURE 1-1

### 1 INTRODUCTION

### 1.1 PURPOSE

The objective of the program was to perform research on new display mechanization concepts and to develop a completely solid state display device. Such a display would involve the use of several basic concepts in display and materials technology. The major concept employed is the generation of moving column displays which have no physically moving parts. This was accomplished, in this program, by the use of electroluminescent (EL) display lamps and solid-state control of the individual elements. Concepts in the design of the control switching of the display are also quite important. These can effect the response time of the display as well as the general quality of the display. This program employed a parallel access, photoconductoractivated control technique that was unique to this type of vertical scale display. The concept of using contrast, rather than brute force, brightness to make the EL display visible is used in this display system. The efficiency of such a technique is of the utmost importance to most EL displays. Display lamps made employing this concept can be derated considerably while providing very good maintainability and almost complete freedom from catastrophic failures.

Such a display system has several unique advantages that qualify it for an important place in the inventory of display techniques for advanced aerospace vehicles. Of prime importance is the advantage of increased reliability. Since most of the technology is new and relatively few devices have been built (and even fewer life tested), the increased reliability is based on the physics of the phenomenon and limited testing. Unquestionably the potential for increased reliability exists.

Especially important for flight hardware is the decreased size and power dissipation of these display systems. In actual comparisons size reductions of 50% have been shown and power reductions of 76% have been demonstrated. An advantage of no small importance is the ability of these displays to accept digital inputs directly. Due to the increased speed and accuracy, many of the newer aerospace systems are adopting digital techniques in a central data processor. Since the concept for these displays involves mainly graphic art techniques, they have a potential for very low production costs.

There are also some potential limitations for such a display such as developmental costs and complexity. These displays involve new technologies and the development usually involves considerably materials technology research, in addition to the usual electronic system design. However, in most cases the potential value far outweighs the immediate development cost. Care and ingenuity must be exercised in the design of the system as the display is made up of a number of individual display elements, each one of which is separately controlled, as contrasted to a single moving tape. The number of parts cannot be permitted to grow to the point where it creates its own problems. The present system involves the use of photoconductor switching. PC elements present their own limitations in response time, temperature limits, and uniformity.

### 1.2 BACKGROUND

This contract was the second in a series initiated by the Control Systems Research Branch, Flight Dynamics Laboratory, W-P AFB, Ohio, having the overall objective of the development of a new class of completely electronic solid state displays. The first work was done under contract number AF33(616)-7904 and modifications SA/1(62-756) and S2(62-1700). A detailed final report on this contract was published in February 1962. This report is available from the Defense Document Center as publication number RTD-TDR-63-4163.

### 1.2.1 <u>Piezoelectric Control</u>

The initial efforts on this first contract were directed toward the development of a display utilizing piezoelectric crystals for selection and excitation of electroluminescent (EL) segments. By supplying a specific RF voltage to a wedge-shaped crystal, localized resonance is obtained since the resonant frequency of the wedge is a sharp function of geometry. At the particular areas of resonance, an electric field is generated by polarization charges appearing on the surface of the crystal. The effect of the surface charge may be used to excite electroluminescent phosphors. A 31-element (5-bit input) display employing this concept, but with individually tuned crystals rather than the wedge-shaped single crystal, was built. However, numerous problems in fabrication, power consumption, and cost forced abandonment of this approach.

### 1.2.2 DINEPCEL

After the piezoelectric approach to a thermometer display was abandoned, the system that appeared the most feasible and economical

used electroluminescent-photoconductor (EL-PC) switches. This choice was made after a careful evaluation of 14 different switching methods.

As an interim solution to the concept of using thin-film EL-PC switching and logic arrays, a hybrid system was fabricated using a diode matrix to decode the input digital signal, neon lamps that were driven directly from the diode matrix, PC's that were illuminated by these neon lamps, and EL lamps that were switched by the resistance change of the PC elements. The acronym DINEPCEL has been made up from the letters identifying the major components; DIodes, NEon lamps, PhotoConductors, and ElectroLuminescent lamps. The display worked very well and consumed less power than its electromechanical equivalent, although it would be more costly to produce.

### 1.2.3 EL-PC-EL

The next step in the development of solid-state vertical scale indicators was the replacement of the diode decoding matrix and neon lamps with a combination of EL lamps and PC's. This was accomplished by a modification of the matrix design so that the logic is performed in parts, in parallel, rather than by a series combination of EL-PC elements. A display was delivered using this concept and it does perform the switching function satisfactorily. However, it did exhibit some undesirable characteristics traceable to the time it constants of the PC elements. This problem occurred only during a change in the input (display level).

### 2 EL-PC MATRIX

It was the purpose of the EL-PC matrix in these systems previously explored to convert the binary information of the encoder to the thermometer output required by the EL display lamps. The philosophy used in designing the matrix was to devise a logic that utilized a building block approach as much as possible. Specifically this years' program was to start from the foundation laid by the programs described above and to develop a system using thin-film technology as much as practically possible.

The block diagram of the EL-PC matrix is shown in Figure 2-1. It will be seen to consist of four basic parts: three-bit translator, the address circuitry, the hold circuitry, and the display lamp itself. Considering the display lamp first, it will be seen to consist of 128 lines, or segments. The total length of the display is four inches which provides a resolution of 32 lines per inch. The problem then was to properly select and excite all of the desired segments.

### 2.1 LOGIC

If the 128 lines are broken into groups of eight, it will be found that there are a total of 16 groups. It is the purpose of the address circuitry to select the group of eight that is at the top of the pointer, as required by the binary input number. To accomplish this, the address circuitry uses all input bits from the fourth up. Within the group of eight selected, one up to seven lines will be selected by the three-bit translator. For this, the three-bit translator requires the first three bits of input information. All groups of eight below the selected block are turned on by the hold circuitry.

It will be observed that the three-bit translator can light up to seven elements. If the input information requires eight elements to be lit, the three-bit translator is inactivated and the hold circuitry causes the entire block of eight to be energized. A more detailed description of the various circuitry is given below.

### 2.1.1 Three-Bit Translator

By referring to the detailed diagram of the three-bit translator in Figure 2-2, it will be seen that each input line lights one lamp. Associated with each lamp are four to seven PC's. These PC's are connected in a series parallel network such that, as the binary input number advances from one to eight, excitation will be provided at the output lines for segments one to seven from the bottom toward the top. The excitation on these output lines is presented to all groups of eight

EL-PC MATRIX BLOCK DIAGRAM FIGURE 2-1

5

THREE-BIT TRANSLATOR SCHEMATIC FIGURE 2-2

pointer elements simultaneously. However, the only pointer elements that actually receive excitation will be determined by the address circuit.

It is evident, by referring to Figure 2-1, that each of the pointer elements is controlled by two PC's -- one on the right and one on the left. The PC on the left is excited by a large EL lamp which, in turn, is controlled by the address circuitry. It will be seen that the groups of seven PC's are all excited by the single larger lamps. Only one of the large EL lamps will be selected at a time; thus, the loading of the three-bit translator is always limited to one block of seven elements. Of course, in the design of this system it is necessary, to consider the loading of all of the other parallel paths even though they are not excited at a particular time. It will be observed that all elements above and below the selected block will not be excited unless they are excited by some other means.

### 2. 1. 2 Address Circuitry

There are two types of select circuitry -- the Address Select and the Hold Select. The detailed circuit diagram for the address select circuitry is presented in Figure 2-3. It is seen to be an extension of the same concepts developed for the three-bit translator, except that, instead of a thermometer (or bar graph) type output, a single line output is achieved. This is entirely analogous to a diode decoding matrix. The input lines control EL trigger lamps as shown in Figure 2-3 these, in turn, illuminate various PC gap areas. Then, depending on the series/parallel combinations, a conductive path will occur for one, and only one, output line.

The output from the address select circuit is used to excite an address trigger lamp which, in turn, illuminates a block of seven PC gaps (out of each block of eight EL pointer segments) on the address PC substrate (see Figure 2-8). These gaps act as gates for allowing power to pass from the three-bit translator to the EL pointer segments.

### 2.1.3 Hold Circuitry

The hold circuitry also consists of two basic sections -- the hold select and the hold sections. The function of the hold select circuit is different from the address select circuit in that it is not selecting a single block but rather all blocks from the bottom of the readout up to, but not including, the block selected by the address select circuit. Logic-wise it is similar to the three-bit translator in that it provides a multiple line selection rather than a single line.

ADDRESS SELECT CIRCUIT FIGURE 2-3

As in the case with the address select circuit, each output line excites an EL trigger lamp, but now the trigger lamp is associated with the hold circuit. In this case, a block of eight gates is illuminated with power being continuously applied to all eight, so that when the gates are opened the eight associated pointer segments are excited immediately.

A binary eight will cause the first trigger lamp to turn on, thereby gating on the bottom eight segments of the pointer lamp. A binary 16 will cause the first two trigger lamps to turn on, thereby causing the bottom 16 pointer segments to be lighted. And so on with a progressively increasing signal, by multiples of eight, until the entire pointer is on.

This portion of the logic uses the fourth to seventh input bits, inclusive, and ignores the first three bits. As mentioned above, the first three bits are used by the three-bit translator for filling in the top of the scale.

### 2.2 PC SUBSTRATES: THREE-BIT TRANSLATOR

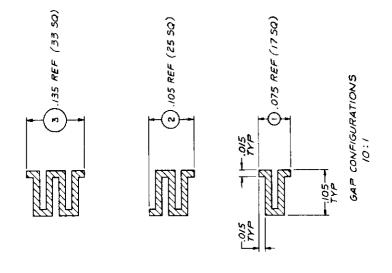

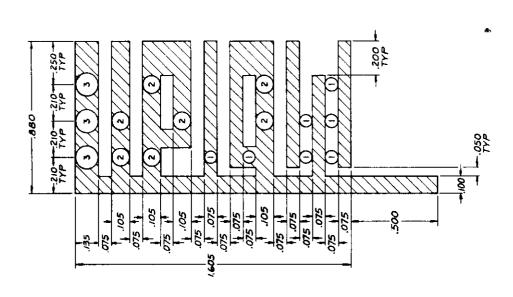

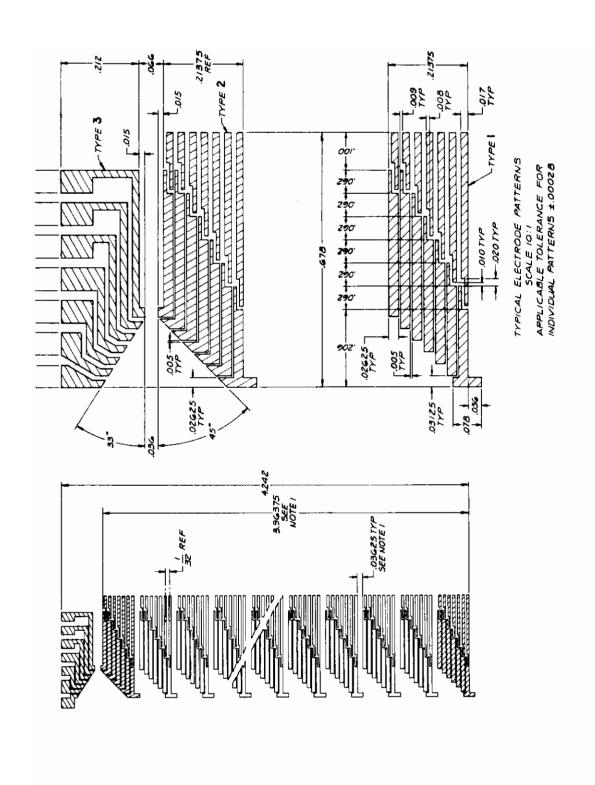

Figure 2-4 shows the electrode pattern of the three-bit translator. There are three EL trigger lamps that are associated with the photoconductor pattern, each of which is about 1.6" long and 0.88" wide. They are mounted lengthwise over the electrode pattern so that the photoconductive gaps are covered, as shown in Figure 2-2.

As an example, a binary one (001) will cause the right hand lamp to light. All PC gaps under that lamp will be in a low impedance state. It will be seen that a conductive path exists from the bus bar on the left to the output terminal on the right for the bottommost output line. A binary two (010) will provide a conductive path for the two bottommost output lines. As the binary number increases to seven (111) output lines are successively energized. Various series parallel combinations of PC gaps as shown are required to accomplish this.

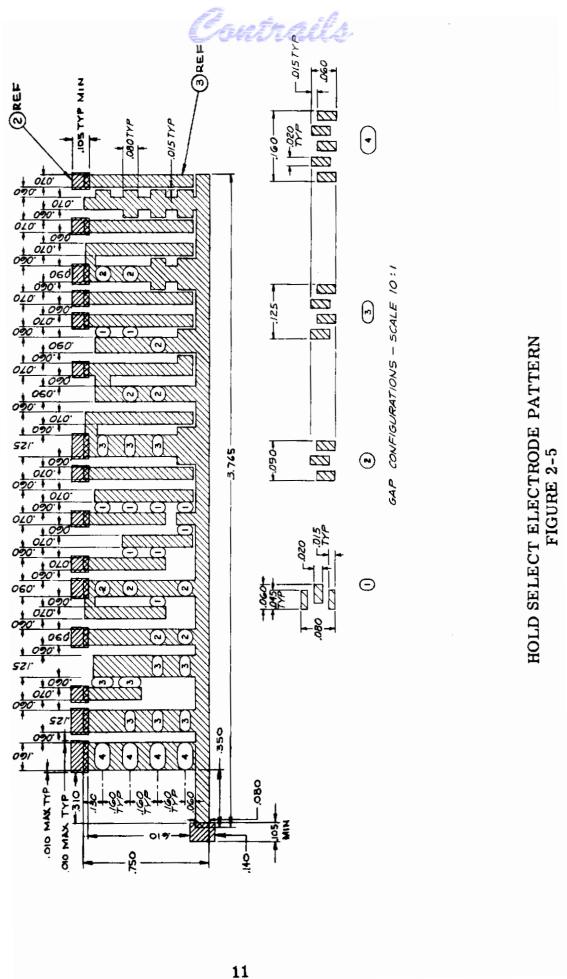

A hold select electrode pattern is shown in Figure 2-5. This is seen to be an extension of the above concepts and is obviously more complex since it uses four EL trigger lamps and provides switching for four bits of input information.

The address select electrode pattern (Figure 2-6) is very similar to the hold select but differs in that only a single line at a time output is provided.

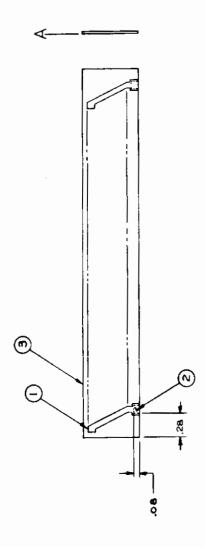

A typical trigger lamp for use with these PC substrates is shown in Figure 2-7.

THREE-BIT TRANSLATOR ELECTRODE PATTERN FIGURE 2-4

ADDRESS SELECT ELECTRODE PATTERN FIGURE 2-6

EL TRIGGER LAMP FIGURE 2-7

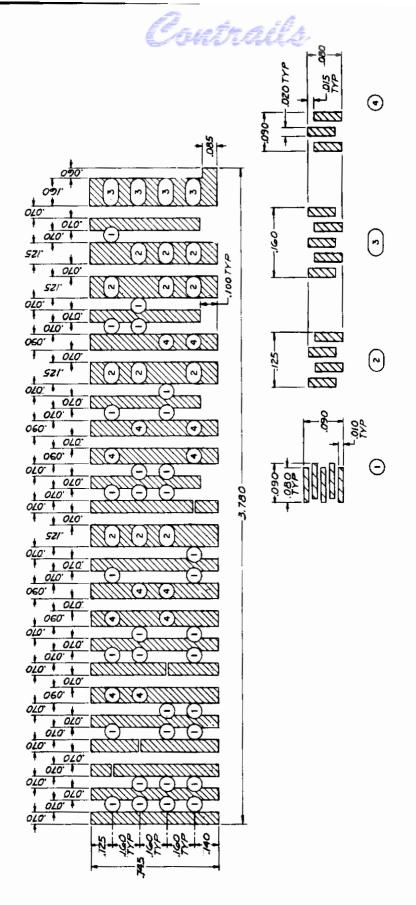

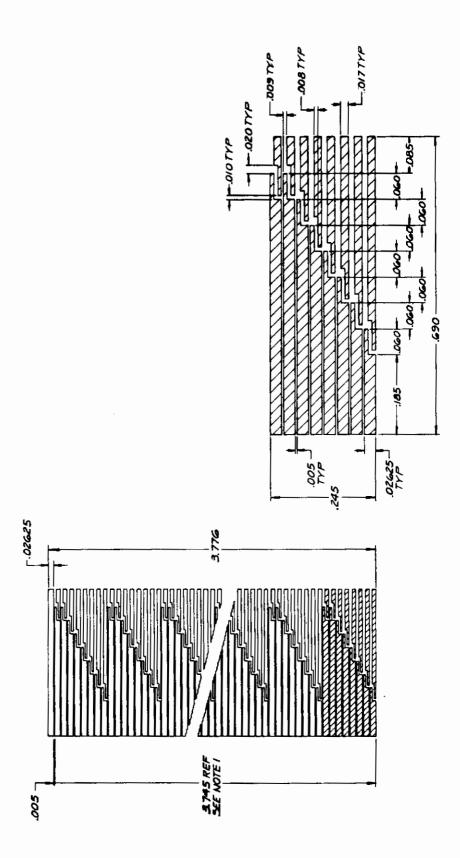

Figures 2-8 and 2-9 show the address and the hold substrates, respectively. Examination of the drawings shows that the address gaps are separated into groups of seven, while the hold gaps are in groups of eight. The same trigger lamp layout (Figure 2-10) is used for both, however. The hold substrate is arranged so that a bus bar can be placed along the input side to provide power to each gap. The tab for each input, within a group of 8, is of a different length. This pattern is repeated for each of the 16 groups of eight tabs in order to simplify the interconnections since all tabs having the same position within a group are connected together. An insulating material is placed over the unprotected tabs with openings wherever a connection is to be made. Seven bus bars are deposited to make the connections between all the tabs occupying the same position in each group.

### 2.3 DISPLAY LAMP

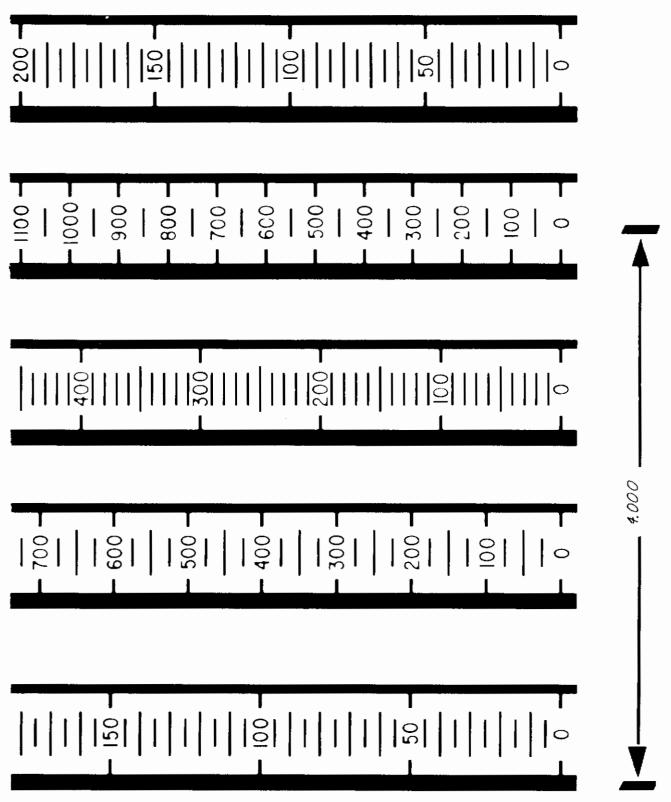

The display lamp as originally conceived was a plastic dielectric EL lamp on a glass substrate. It was provided with multiple parallel co-planar back electrodes so that individual lines could be excited with a resolution of 32 per inch. Scale markings were to be silk screened on the front of the lamp and are shown in Figure 2-11 for the five different channels.

### 2.4 ELECTRONICS SYSTEM

A block diagram of the electronics system as originally envisioned is shown in Figure 2-12. It is seen to be quite simple and straightforward. A manually operated U-scan shaft angle encoder provides a binary input signal to a group of SCR switches that directly controls the trigger lamps of the address select, hold select, and three-bit translator circuits.

### 2.5 SHAFT ANGLE ENCODER AND DRIVER

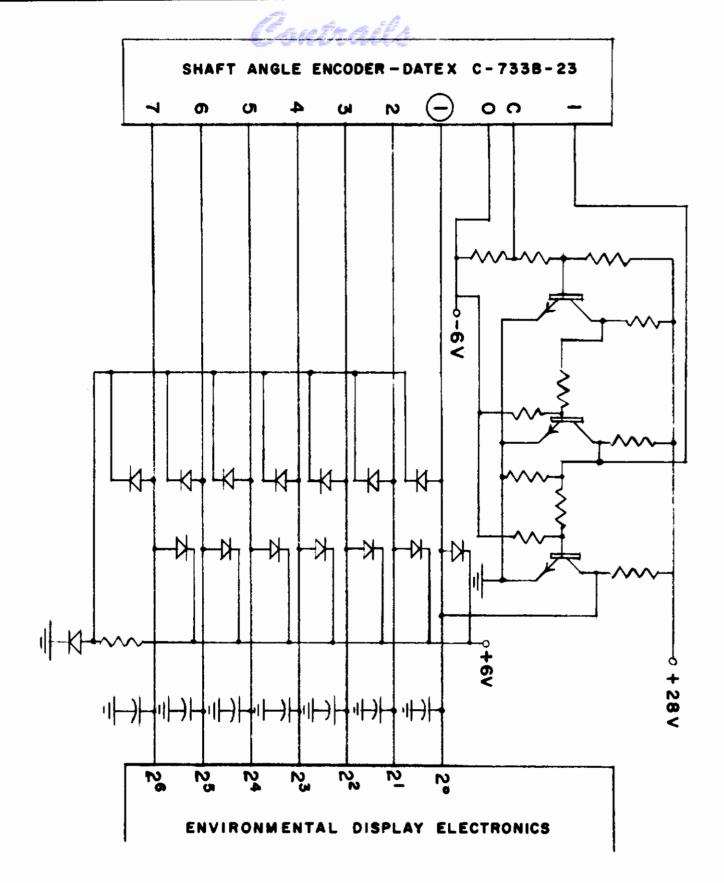

The shaft angle encoder is a Datex Model C-733B-23. This is a seven-bit U-scan encoder, with 128 counts, straight binary output.

The schematic for the encoder drive is shown in Figure 2-13. It continuously senses the least significant bit and provides this output and its inverse. These two signals are then fed back into the encoder and provide power for the remaining output lines. The advantage of using a U-scan encoder is that there is no diode voltage drop stack up as is encountered in a V-scan encoder.

ADDRESS CIRCUIT ELECTRODE PATTERN FIGURE 2-8

HOLD CIRCUIT ELECTRODE PATTERN FIGURE 2-9

# TRIGGER LAMP LAYOUT FOR THE ADDRESS AND HOLD CIRCUITS FIGURE 2-10

SCALE MARKING FOR THE FIVE CHANNELS

# ORIGINAL ELECTRONIC SYSTEM BLOCK DIAGRAM FIGURE 2-12

### 2. 6 SCR SWITCHES

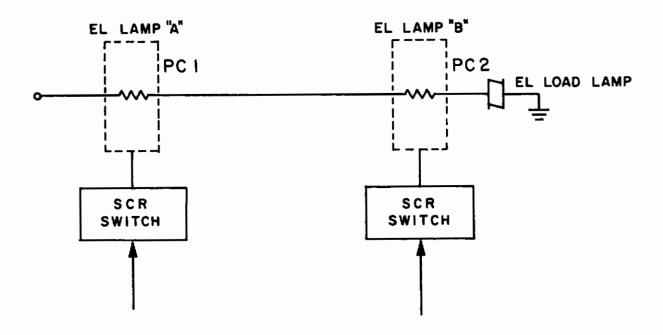

A new AC switch, utilizing high voltage SCR's especially specified for this usage, was designed for controlling the EL trigger lamps. This circuit, shown in Figure 4-9, is seen to consist of two 400 volt SCR's in parallel, plus associated circuitry.

When the first SCR is turned on, it permits capacitor, C, to acquire a charge during the initial half cycle of the AC excitation. This charge then discharges into the gate of the second SCR during the second half cycle, thus providing full wave control of the AC power.

The EL lamp may be either in series with the SCR's or in parallel with an SCR. The latter method is preferred since the EL lamp is shorted to ground when it is in the off state, thereby eliminating any chance capacitive pickup.

ENCODER DRIVER CIRCUIT SCHEMATIC DIAGRAM FIGURE 2-13

This description of the electronics system is as it was originally planned, although the electronics system was never constructed in its entirety because of difficulties that were encountered when the EL/PC matrix was assembled.

These problems were centered around the response times of the PC's and exhibited themselves as transient flickering and flashing when the input information was updated. In some cases segments and areas above the correct output level would flash on momentarily as the system adjusted to a new input code. In other cases, segments and areas below the indicated level would momentarily be extinguished, again while the system was adjusting to a new input. The reason that these phenomena occurred are covered in the following section.

### 3 EL-PC SYSTEM ANALYSIS

To provide an understanding of the problem encountered in the EL-PC system, a brief presentation of various pertinent parameters of EL lamps and photoconductive cells will first be made. Then the action obtained when the two are combined is examined.

### 3.1 EL LAMPS

The characteristics of EL lamps of interest are:

- a. the dependence of brightness on voltage

- b. turn-on time

- c. lamp impedance

Operation is at a constant 400 cps and, therefore, is not a factor; and since the problem occurred when all components were new, life is disregarded. Color of the emitted light could be a factor, but since there is but little color variation for a given lamp structure it is considered to be constant. The brightness wareform has a large AC component in it; however, since the PC has a long time constant relative to the AC component, and since all PC measurements are taken with EL excitation, this, also is not considered to be a factor.

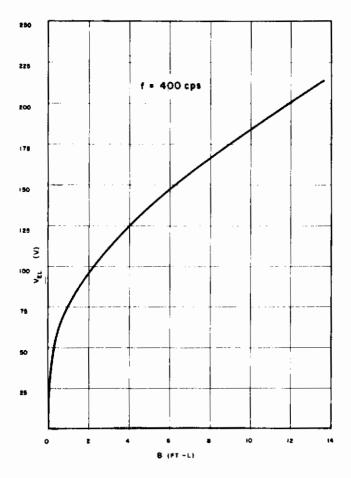

A curve of lamp brightness vs lamp voltage is given in Figure 3-1.

If an AC voltage is suddenly applied to an EL lamp, it normally requires several cycles of the applied voltage before maximum brightness is reached. This is essentially independent of the frequency of the power source and is usually from 3 to 6 cycles. At 400 cps this means that from 7.5 to 15 milliseconds are required to achieve full brightness. When the voltage is suddenly removed, the light output decays in about one-half cycle of the supply frequency.

The impedance of an EL lamp is dependent on several factors:

- a. type of lamp structure

- b. operating frequency

- c. size of the active area

- d. applied voltage

For this analysis, the lamp impedance of the actual trigger lamps were measured so as to provide a good working base.

APPLIED VOLTAGE VS. EL BRIGHTNESS CURVES FIGURE 3-1

### 3.1.1 Photoconductors

As the PC's are used to turn lamps on and off, it was felt desirable to establish impedance limits which would insure that the EL lamps were turned on to a high enough brightness level, or were turned off to a sufficiently low level. Since the PC's are in series with the EL lamps they form a voltage divider. Then, knowing the lamp impedance, its voltage-brightness curve, the applied voltage, and the acceptable lamp brightness limits, it is possible to calculate the PC impedance limits.

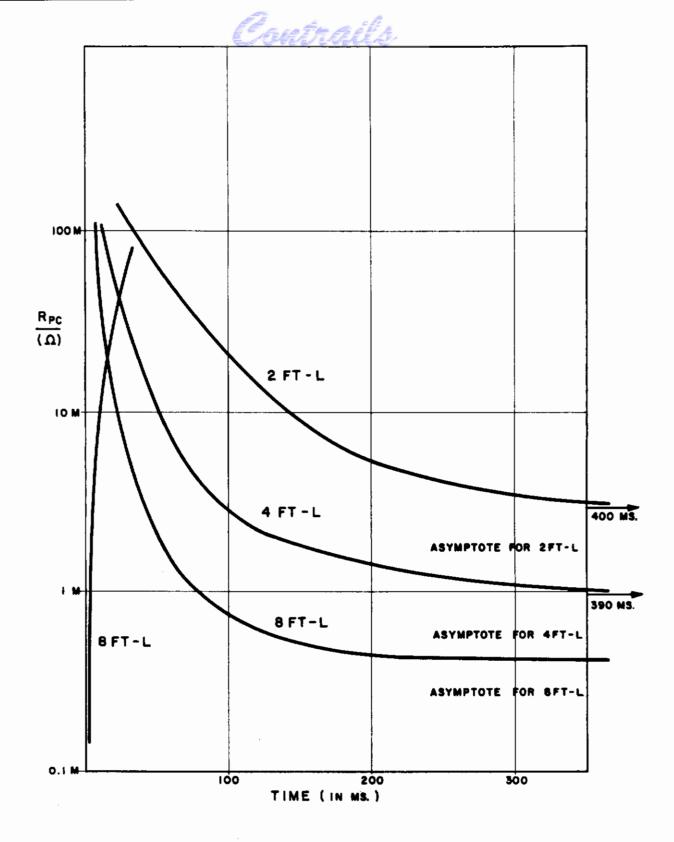

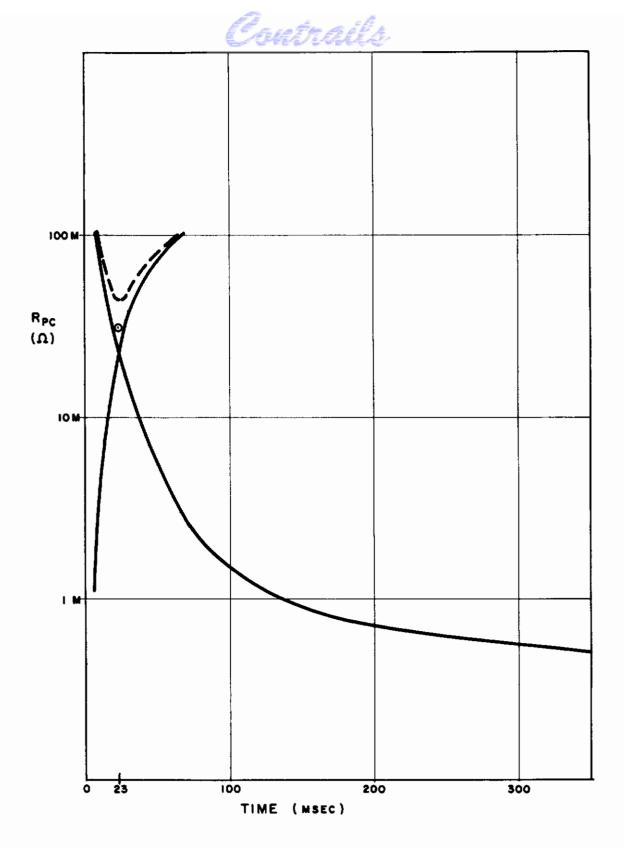

The next factor of importance is response time. (Here, a means to measure response time had first to be developed since there was some question as to whether measurements taken under DC conditions would be valid for AC usage.) Further, the response time is of extreme importance since it determines how rapidly the associated EL lamps turn on or off. Typical curves are shown in Figure 3-2 for various levels of trigger lamp brightness.

TYPICAL TIME RESPONSE CURVES FOR PHOTOCONDUCTORS FIGURE 3-2

Other factors which could possibly enter into the analysis include voltage dependence of impedance, wavelength of the incident light, uniformity of PC characteristics along a substrate, and electrode configuration. Although some information sources have indicated the existence of a voltage dependence of resistance, the PC vendor indicated that none has been observed on his photoconductors, and observations to verify this were in agreement. Therefore, voltage dependence was not considered.

Since EL trigger lamps are used as a light source, the incident light was assumed to be of constant wavelength and not an essential parameter.

In regards to the uniformity of the PC characteristics, limits were placed on the PC impedance over the entire surface. However, difficulty in achieving uniformity of impedance was experienced.

Finally, for a given photoconductive layer, the actual impedance of a given electrode configuration will depend on the length and width of the illuminated area. This is a design parameter and must be considered during layout of the electrode pattern. It is a factor which must be considered in the analysis. Typical electrode patterns are shown in Figures 2-5, 2-6, 2-8, and 2-9. It will be observed that not all gaps have the same area. This is because various combinations of PC switches are used to turn on a given EL lamp. The electrode gaps are designed so as to assure turn on under worst case conditions. As a result, different combinations can provide widely different impedances; and this, in turn, has a marked effect on overall response.

### 3.2 THE PROBLEM

After the display was assembled, operation under static conditions were quite good. It was not until a change in the binary digital input signal occurred that difficulty was encountered, and even then it depended on the change. Visually, when a change in input occurred, the new information would be displayed and simultaneously some display segments above the indicated output would flash on for just a few milliseconds, but long enough to be very disturbing.

With some other input changes, some of the display segments below the indicated output would flash off and then on again. This, too, was very disturbing. The source of the difficulty is explained in principle in the following section.

### 3.2.1 Transient Analysis

Consider the case of two PC's and an EL lamp connected in series as shown in Figure 3-3. It is necessary to assume some operating conditions:

- a. A supply voltage of 200 volts rms is applied to the EL-PC network.

- b. The trigger lamps for driving the PC's have a brightness of 4 foot-Lamberts when turned on.

SERIES EL-PC SWITCHING CIRCUIT FIGURE 3-3

- c. The photoconductors have a response characteristic as shown in Figure 3-2 (it is assumed that the PC gaps are identical).

- d. The EL load lamp has a voltage-brightness characteristic as shown in Figure 3-1. (It will be assumed initially that the EL lamp brightness follows the applied voltage with no time delay.)

- e. The EL lamp is taken to have an impedance of 10 megohms.

The above assumptions are based on data obtained during the course of the project.

Consider the case where one input trigger lamp (say "A" is on and the other ("B") is off. Referring to the 4 ft-L curve of figure 3-2, the "ON" impedance for two gaps in series is 910K. Each gap then has an "ON" impedance of 455K. The dark impedance of each PC is very high, in the order of 300 megohms.

It will be noted in Figure 3-2 that only one curve is indicated for turnoff. This is because no significant difference in the turn-off curve was

observed with variations in light level if the "ON" impedance is used as

a starting point. This curve is modified for a single gap in Figure 3-4.

If trigger lamp A is suddenly turned off and lamp B is simultaneously turned on, the resistance of gap A will follow the turn-off curve and the resistance of gap B will follow the turn-on curve. At any instant the total impedance of the photoconductor is the sum of the two. This is the dashed line in Figure 3-4. It is seen that the impedance of the PC falls to 44 megohms. If the voltage across the EL lamp is now calculated (remembering that it is essentially a capacitor) it is found to be 43 volts. From the curve of voltage vs brightness (Figure 3-1) this is seen to provide a transient flash of about 0. 2 ft-L. This is sufficient to be objectionable; however, if the PC resistance had been above 50 megohms, no flash would be evident.

One assumption made was that the EL lamps turn on instantly. This is not true in reality. The effect would be that lamp A would turn off immediately and gap A would increase in resistance, but lamp B would come on in about 10 milliseconds, thereby slowing down the turn-on of gap B slightly. In all probability the series resistance would never fall below 50 megohms and no flash would occur. This configuration may then be considered to be marginal.

If the case is now considered of three gaps in series, it is evident that each gap must go to a lower impedance to assure sufficient voltage to the output lamp when all are "ON". The only effect on the

# PHOTOCONDUCTOR RESPONSE FOR A SINGLE GAP FIGURE 3-4

response curve is to slide it down the resistance axis to the new "ON" level. It will have the same shape. If one trigger lamp (say C) is held on continuously and lamp A and B are switched as before, the same transient condition will occur but the series impedance will reach a much lower level (29 megohms). Going through the same calculations as before, a transient flash of 0.5 ft-L will occur which cannot be removed even by delays in turn-on of EL trigger lamps. (Note the arrow in Figure 3-4.)

By similar reasoning the parallel and series-parallel cases can be considered with the same type of result.

As a result of the above analysis it was concluded that the use of this type EL-PC logic switching was unsatisfactory. A number of possible variations of EL-PC logic and alternative methods were considered as listed in Table 1 with various comments. As a result of these considerations the system described in the following sections evolved.

#### 3. 2. 2 Final Configuration Diode Transistor EL-PC Logic

A hybrid system using diodes-transistors and EL-PC logic was used to minimize the transient problems previously described.

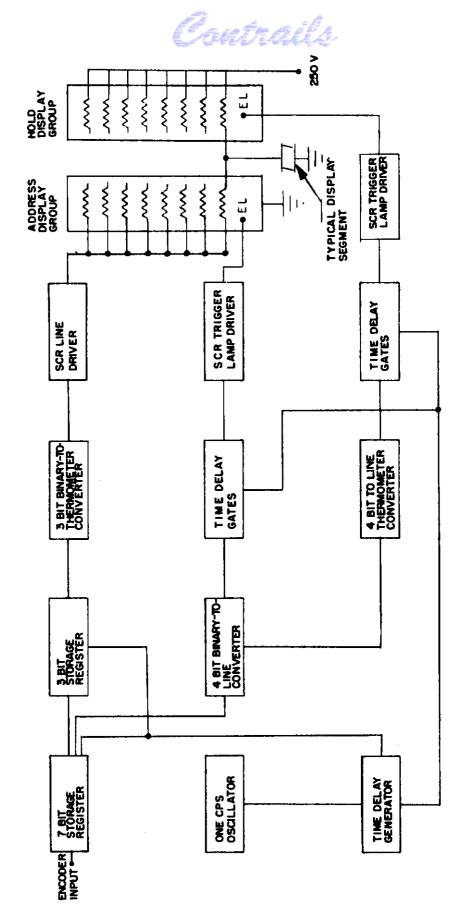

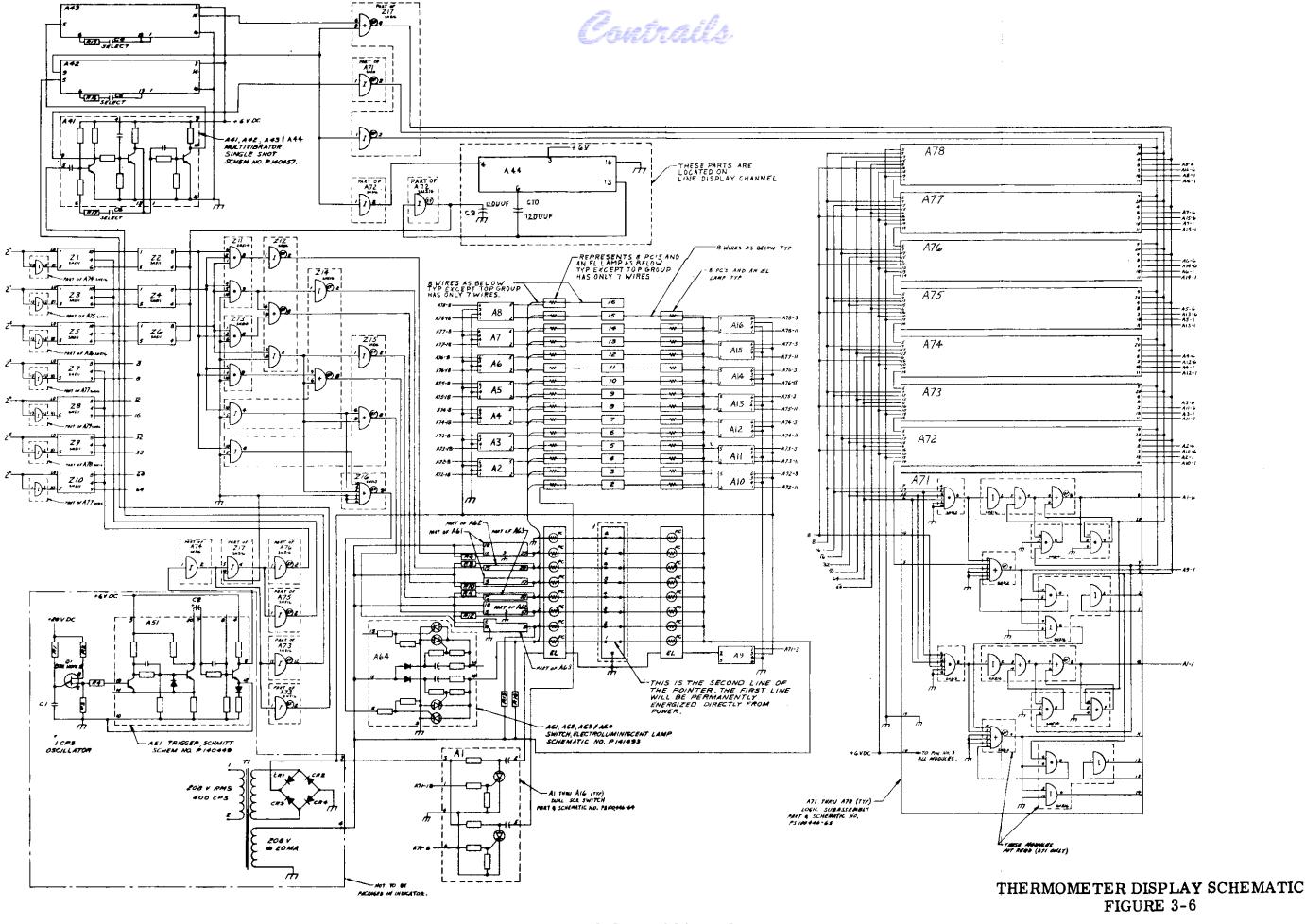

The logic to convert from a binary input to a thermometer display can best be described by reference to Figure 3-5. The complete schematic is shown by Figure 3-6.

The seven-bit input from the U-scan shaft encoder is fed in parallel to the input storage register. This input is updated at a rate of one cycle per second. The clocking signal for the updating is generated in the oscillator.

THERMOMETER DISPLAY BLOCK DIAGRAM FIGURE 3-5

# TABLE 1 EL-PC LOGIC SWITCHING ANALYSIS (Page 1 of 3)

| 1. | Non-inhibit logic - fast |

|----|--------------------------|

|    | substrates only.         |

- a. Response greater than 100 milliseconds.

- b. Flickers.

- 2. Non-inhibit logic slow

Address and Hold substrates.

Fast Address and Hold Selects.

- a. Slow response 300 to 400 milliseconds.

- b. No flicker except on 3 bit.

- c. Can't handle rapidly changing inputs.

- 3. Inhibit logic fast substrates only.

- a. Response greater than 100 milliseconds.

- b. Flickers.

- 4. Inhibit logic slow Address and Hold substrates. Fast Address and Hold Selects.

- a. Same characteristics as 2.

- 5. Extra EL-PC buffer between trigger lamps and Select substrates.

- a. Slow response.

- b. No flicker

- c. Doesn't gain anything over2 and 4.

- d. Add complexity to build.

- 6. Bi-stable circuit between trigger lamps and Select substrates.

- a. Fast substrates can be used.

- b. Response time of bi-stable is added to overall response.

- c. Can be made insensitive to flicker from Select substrates.

- Much added complexity more space required.

# TABLE 1 EL-PC LOGIC SWITCHING ANALYSIS (Page 2 of 3)

- 7. Turn-on delay for SCR's.

- Removes flicker within limits.

- b. Different inputs to a pattern have different response times.

- c. Requires a very high capacitance.

- d. Increases cost of SCR because of tightened specifications.

- e. Represents a fictitious input for a short period of time.

- 8. Varistor between trigger lamps and Select substrates.

- a. Could be either deposited on lamps or discrete components.

- b. Can remove flicker.

- c. Slows response because fast response region cut off.

- d. More data needed.

- e. Impedance of material is important - must be matched.

- f. Availability may be a problem.

- 9. Zener instead of varistor.

- a. Same characteristics as varistor.

- b. Impedance matching problems.

- 10. Trigger diods instead of varistor.

- a. Same comments as Zener.

- 11. Shockley diode instead of varistor.

- a. No loss of speed.

- b. No flicker.

- c. Requires a minimum current.

- d. Power dissipation high.

- 12. Shockley diode relaxation oscillator w/diode matrix.

- a. Low voltage to elbow lamps (approx. 70 V rms)

- b. SCR's on 3 bit.

- c. Fewer parts than SCR's

- d. Being checked for response.

- e. No adjustment for lamp decay.

- f. Packaging.

- 13. PC matrix to SCR's controlling trigger lamps.

- a. No flicker.

- Uses what has been completed.

- c. Requires space 38 additional SCR circuits per display.

- d. Lower cost.

- 14. Diode matrix to SCR's controlling trigger lamps.

- a. No flicker.

- b. New packaging more space required.

- c. Lower cost.

The output from the seven bit storage register goes to the three bit storage register and also to the four bit binary-to-line converter.

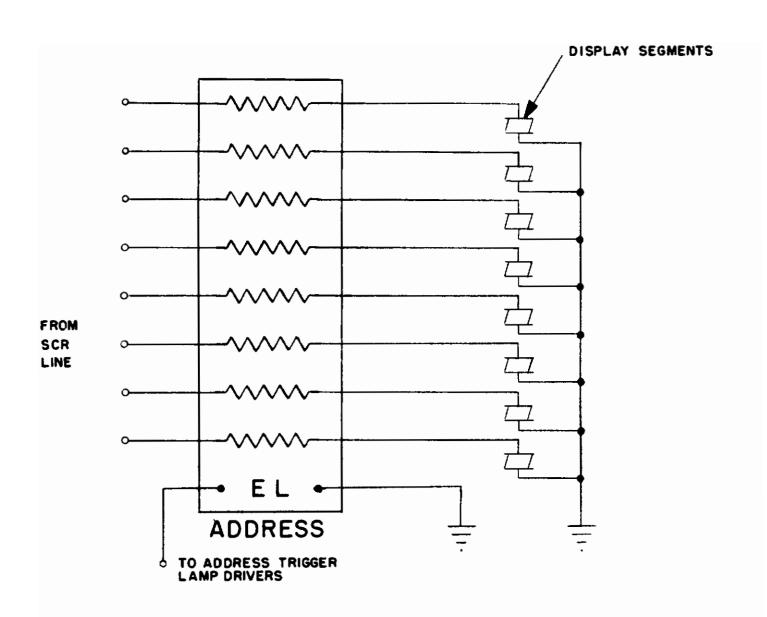

The information fed to the three bit storage register is used to drive the seven lines of each address display group. A clocking signal for the three bit storage register comes from the time delay generator and is timed to prevent transient flashes. Timing problems are explained in more detail in Section 4.4. The address display group consists of eight EL display segments, each of which is in series with a photoconductor. Silicon-controlled rectifiers are used to switch the voltage necessary to excite the display segments.

The four-bit binary-to-line converter provides the logic for proper addressing of the address display groups. Time delay gates are used to compensate for the response time of the photoconductors of the EL-PC matrix. Silicon-controlled rectifiers are used to switch the voltage necessary to excite the address trigger lamps.

Information from the four-bit binary-to-line converter is fed to the four bit line-to-thermometer converter. This converter provides the logic for proper selection of the hold display groups. Time delay gates are also used to compensate for the response time of the photoconductors in the EL-PC matrix. Silicon-controlled rectifiers are used to switch the voltage necessary to excite the hold trigger lamps.

The thermometer display is, therefore, obtained in the following manner. If, for example, a binary encoder number of 10010 was to be displayed, the line drive logic (includes a binary-to-thermometer converter) would excite the first two segment lines of each address group. The address drive logic (includes a binary-to-line converter) would excite the third address EL trigger lamp, thus turning on the first two segment lines in the third address group. At the same time the hold drive logic (includes a line-to-thermometer converter) would have turned on the hold EL trigger lamps which excite the two hold groups below the two lit segments. The display segments are now lit up to and including the segment corresponding to 10010.

#### 4 CONVERSION LOGIC

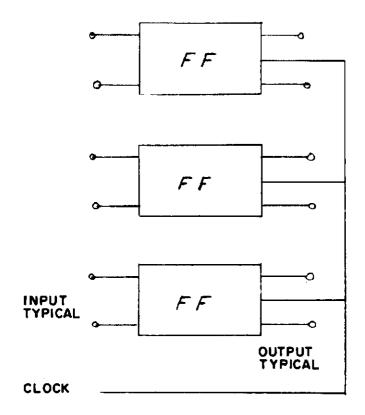

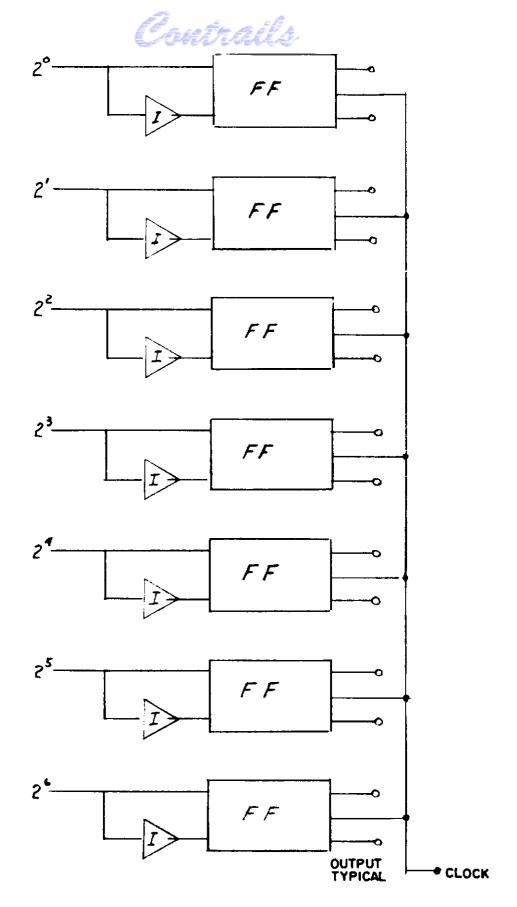

#### 4.1 STORAGE REGISTERS

Both the three-bit storage (shown in Figure 4-1) and the seven-bit storage registers (shown in Figure 4-2) are made up of integrated circuit flip-flops. The updating signal for the seven-bit storage comes from the one cps oscillator through a buffer. The updating signal for the three-bit storage register comes from a one-shot multivibrator in the time-delay generator.

The integrated circuits used are Texas Instrument type SN511 Diffused Silicon Bistable Networks. These networks are designed using the RCTL (Resistor-Capacitor-Transistor-Logic) configuration. This logic selection was chosen to be the most compatible with LSI thin-film microcirucits.

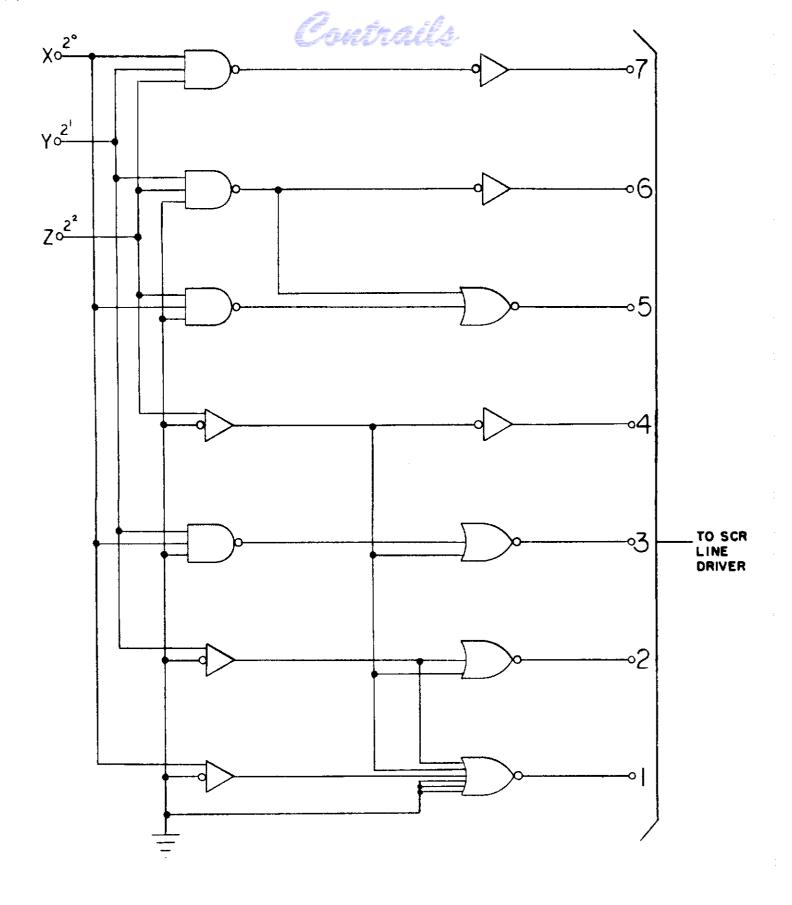

### 4.2 THREE-BIT BINARY-TO-DECIMAL THERMOMETER CONVERSION

Several possibilities existed for providing a low cost, three-bit matrix to make the required conversion. One possibility was to use

THREE-BIT STORAGE REGISTER FIGURE 4-1

SEVEN-BIT STORAGE REGISTER FIGURE 4-2

Burroughs Corporation Bipco modules which are available in many logic configurations. While this method looked very promising, problems existed in providing a compatible interface at both the input and the output.

Another method -- the one which was chosen for the final configuration -- involved the use of integrated circuits. Since most of the original design concepts were based on the use of integrated circuits, this approach was the most feasible from an interface standpoint.

Figure 4-3 shows the three-bit conversion matrix. The matrix is made from combinations of "Nand" and "Nor" gates. With the gates selected, no buffers are required and the gates work directly into the siliconcontrolled rectifier drivers which control the EL line segments.

The Nand and Nor gates are Texas Instrument type SN 513 and SN 516 diffused-silicon logic networks. These networks are designed using the RCTL (Resistor-Capacitor-Transistor-Logic) configuration.

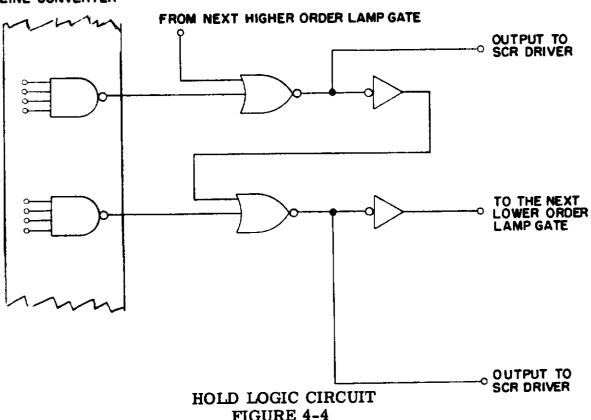

## 4.3 FOUR-BIT LINE-TO-THERMOMETER AND BINARY-TO-LINE CONVERTERS

In order to minimize the number of components the line-to-ther-mometer converter, the binary-to-line converter, and the time constant circuitry were combined. Integrated circuits were used for logic elements. A typical portion of the circuit for the hold logic is shown in Figure 4-4 while the logic for the address binary-to-line converter is shown in Figure 4-5. Typical time delay circuits for delaying turn ON and turn OFF are shown in Figures 4-6 and 4-7.

#### 4.4 TIME DELAY

The time response of the photoconductors is such that it is necessary to use time delays during the updating period. This prevents transient flashing. To make the switching appear as uniform as possible, the following timing scheme was used:

|                                                         | ON                     | OFF                    |

|---------------------------------------------------------|------------------------|------------------------|

| Display Segment Drivers<br>Address Trigger Lamp Drivers | 430 msecs<br>430 msecs | 430 msecs<br>215 msecs |

| Hold Trigger Lamp Drivers                               | None                   | 640 msecs              |

THREE-BIT BINARY-TO-THERMOMETER CONVERTER FIGURE 4-3

The methods for obtaining these time delays are shown in Figures 4-6 and 4-7. Figure 4-6 shows the schematic for delaying the turn ON of the lamp. Figure 4-7 shows the schematic for turn OFF of the lamp. The timing source consists of three one-shot multivibrators with selected timing intervals.

The one-shot miltivibrators are LSI thin-film microcircuits which have been designed to be compatible with the Texas Instrument integrated circuits.

#### 4.5 SCR DRIVER CIRCUITS

Two types of SCR driver circuits are used. The first type, shown in Figure 4-8, uses a single silicon-controlled rectifier to shunt to ground the full wave rectified voltage which supplies the trigger lamps for address and hold. The trigger lamps are OFF when gate current is supplied to the SCR. When the gate current is removed, the SCR turns OFF and the full wave rectified voltage is applied to the EL trigger lamp through a series capacitor.

#### PORTION OF 4 BIT BINARY TO LINE CONVERTER

Page Blank in Original Document

Page Blank in Original Document

The second type is shown in Figure 4-9. It is used to drive the line segments of the display lamp. Two silicon-controlled rectifiers are used to provide AC shunting to ground of the supply voltage. When the logic provides gate current for SCR<sub>1</sub>, the SCR shunts the supply voltage for the positive half cycle of the supply voltage. Energy, which is stored in capacitor C<sub>1</sub> during the positive half cycle, is used to supply gate current for the negative half cycle. On the negative half cycle, SCR<sub>2</sub> is turn ON by C<sub>1</sub> discharging into the gate and thus the negative half cycle is shunted to ground.

#### 4.6 SCR MODULE DESCRIPTION

The full wave rectified SCR driver is packaged in a cord wood configuration using discrete components. Both the packaging and the construction were done at LSI. This technique proved very successful in the modules made for the Incremental Velocity Indicator used in Gemini.

The AC supply SCR driver is a LSI microcircuit containing thin-film resistors and discrete silicon-controlled rectifiers. The vacuum deposited resistors have proven very stable over life and temperature extremes.

#### 4.7 EL-PC SWITCHING

The method of switching the segment display lines with EL-PC switching is shown in Figure 4-10.

The excited lines of the address display groups are prevented from coming on by the high impedance of the PC switches. The same holds true for the hold lines. When either an address trigger lamp or a hold trigger lamp is turned ON, the corresponding PC's go to a low impedance and the proper display segments are lit.

Uniformity of the photoconductors is a very important consideration. It determines the brightness characteristics of the display segments. The non-uniformity of the PC's can become quite noticeable when going from an address group to a hold group if the differences are quite large.

Time response of the PC is another important consideration. The possibility of transient flashes exists when switching due to the inherent delays in the PC's.

The time delay circuits described in Section 4.4 are designed to compensate for possible undesirable transients.

## SCR FULL WAVE SUPPLY DRIVER CIRCUIT FIGURE 4-8

SCR AC SUPPLY DRIVER CIRCUIT FIGURE 4-9

Page Blank in Original Document

LINE DISPLAY BLOCK DIAGRAM FIGURE 5-1

Page Blank in Original Document

The integrated circuits used are Texas Instrument type SN 511 Diffused Silicon Bistable Networks. These networks, designed using the RCTL configuration, were chosen to be the most compatible with LSI thin-film microcircuits.

#### 5.3 FOUR-BIT BINARY-TO-LINE CONVERTER

The four-bit binary-to-line converter is shown in Figure 4-5. Texas Instrument types SN 516 and SN 513 Nand/Nor gates are used to provide the logic for the line output. The outputs are used to drive the SCR line driver modules.

#### 5.4 SCR DRIVER CIRCUITS

The two types of SCR driver circuits used are described in Section 4.5.

#### 5.5 TIME DELAY

The only time delay required for the line display is incorporated in the three-bit binary-to-line converter. All outputs from the converter are delayed approximately 200 milliseconds for the segment light coming ON. There is no delay for turn OFF. This time delay prevents transient flashing when the address display groups are being switched.

A LSI thin-film microcircuit one-shot miltivibrator is used to obtain the 200 milliseconds delay time. This module was designed to be compatible with the Texas Instrument type SN 511 flip-flops which are used in the storage register.

#### 5.6 EL-PC SWITCHING

The method of switching the segment display lines with EL-PC switching is shown in Figure 5-4. The excited line of the address display groups are prevented from lighting the segments by the high impedance of the PC. When an address group trigger lamp is excited, the corresponding groups of EL lamps are turn ON and the proper segment is displayed.

Impedance uniformity of the PC's becomes an important consideration since it determines the brightness characteristic of the display segment being lit. Another important consideration is the time constant of the PC. The time delay circuitry for the three-bit converter has been designed to compensate for time response differences in the PC's.

## EL-PC SWITCHING LOGIC FIGURE 5-4

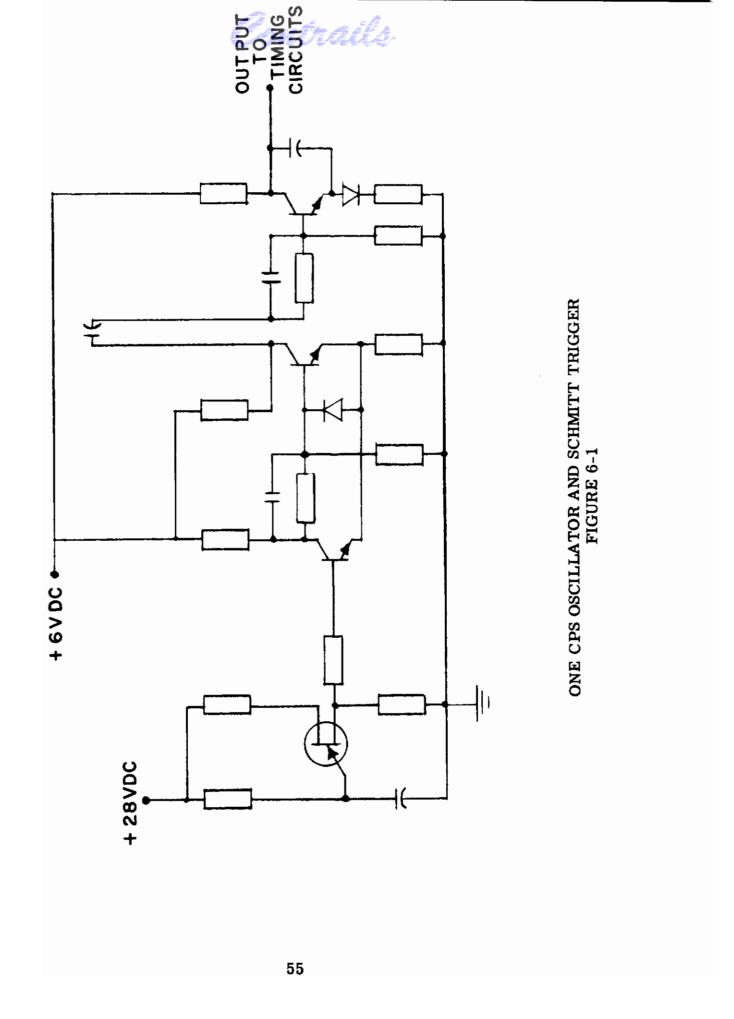

#### 6 POWER SUPPLY

The power supply for the indicator package contains the following components:

| Quantity | Description                                                   |

|----------|---------------------------------------------------------------|

| 1        | +28 V DC power supply                                         |

| 1        | +6 V DC power supply                                          |

| 1        | -6 V DC power supply                                          |

| 1        | One cps oscillator and Schmitt trigger                        |

| 1        | Encoder driver circuit                                        |

| 1        | AC power transformer                                          |

| 1        | Full wave rectified supply for address and hold trigger lamps |

The three DC power supplies were purchased as components from Technipower, Inc. The schematic for one cps oscillator and Schmitt trigger is shown in Figure 6-1.

The encoder driver circuit is shown in Figure 6-2. This circuit is necessary to switch the encoder brushes which are designed to prevent ambiguous counts.

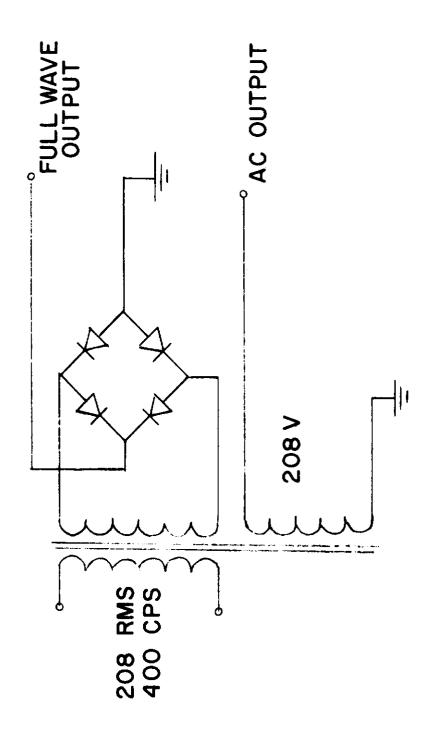

The AC power supply and full wave rectified supply are shown in Figure 6-3.

ENCODER DRIVER CIRCUIT FIGURE 6-2

FULL WAVE RECTIFIED SUPPLY FIGURE 6-3

#### 7 PACKAGING

Each of the five displays is a complete channel. All of the logic and electronics required are built into a separate subassembly along with the EL-PC matrix and display lamps.

Four of the five channels are identical except for the actual display screening. The fifth channel is different only in the reduced number of SCR modules and different logic.

By unsoldering the outer case at both ends (the bezel and the rear cover) it may be slid off, exposing the complete assembly. Any one of the five channels may be removed from the assembly by unbolting it from the bezel and rear cross bracing.

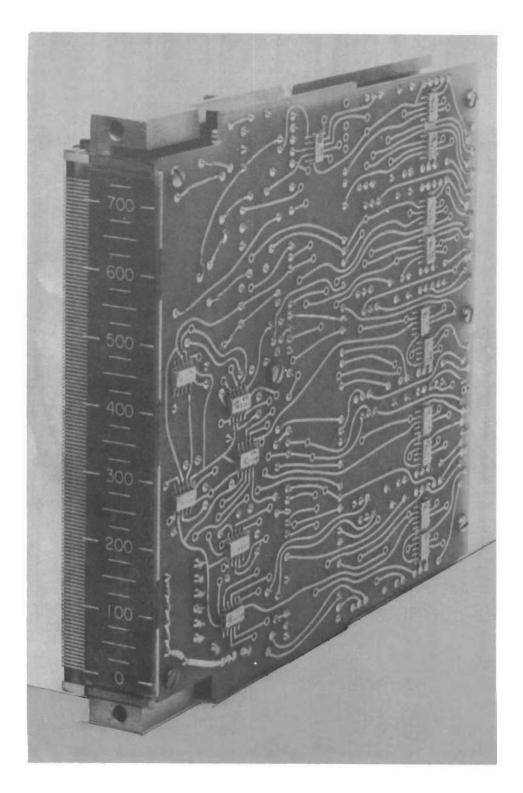

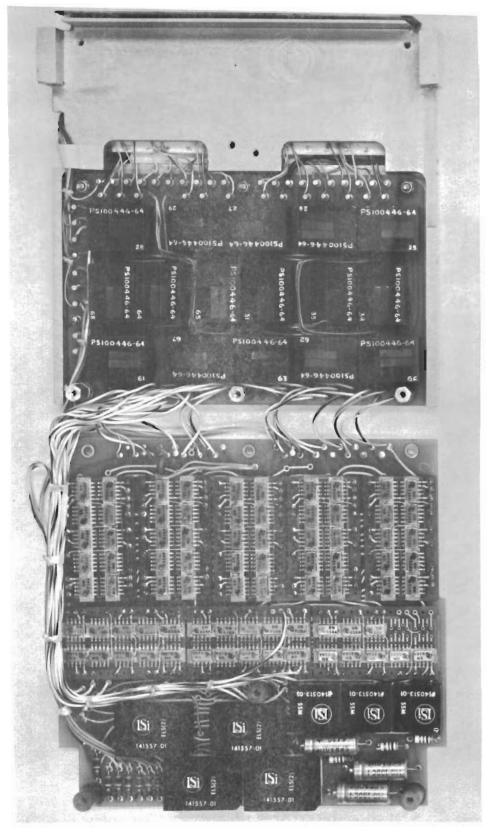

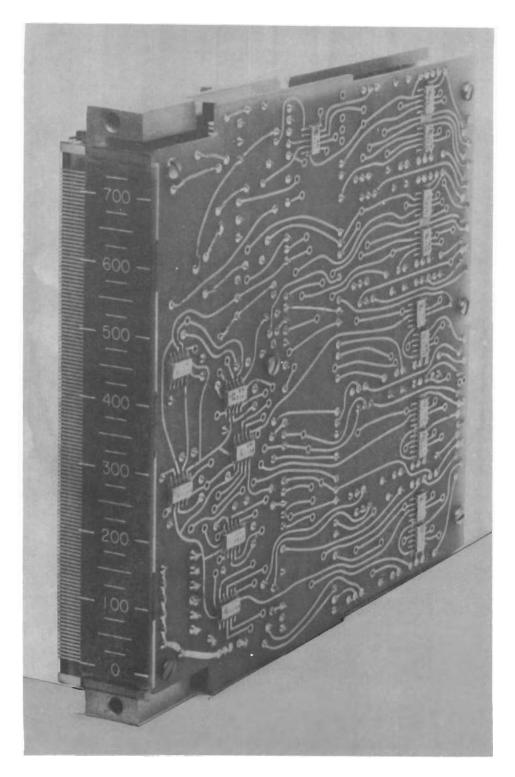

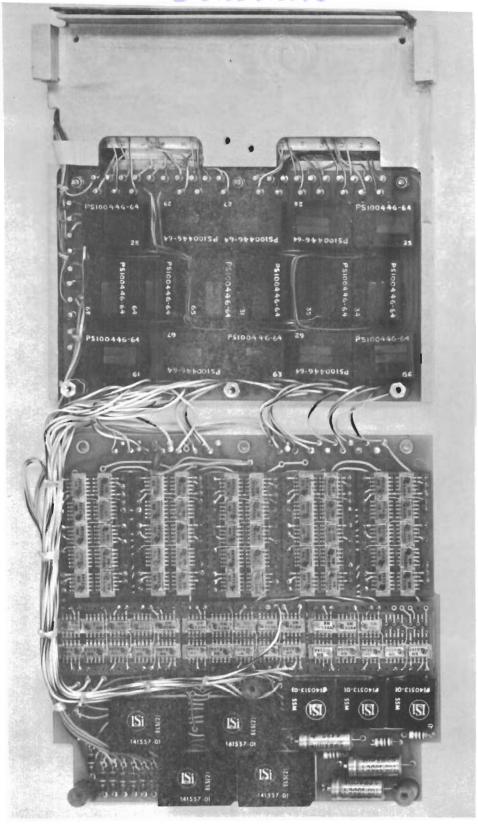

A typical channel ready for attachment to the bezel may be seen in Figure 7-1. Figure 7-2 shows a channel with the logic board folded back to provide a clearer idea of the internal construction. As can be seen from the picture, the channel consists of two printed circuit boards and an EL-PC matrix display subassembly supported by an aluminum frame. The aluminum frame serves not only as a structure but provides a means of heat transfer from the electronic components to the outer case.

One of the printed circuit boards contains all of the trigger lamp switching components. These components are first mounted "cordwood" style, then potted into modules. The modules are then soldered to the printed circuit board.

The remainder of the logic components are mounted on the other boards. These components are a combination of SCR modules (as described in the previous paragraph) LSI microcircuits, and integrated circuits.

The SCR modules and the LSI microcircuit modules are mounted directly to the printed circuit board. The complex interconnect and the necessity of welding the leads of the integrated circuits (IC) led to the design of a multilayer board for submounting the modules.

Ten IC modules are welded to the 1"  $\times$  1-1/2" special nickel outer layer of the multilayer board. The interconnecting circuit uses the conventional copper-clad and plated-through hole approach on the inner layer. These board assemblies are soldered to the main printed circuit board by means of bus wires inserted in the holes provided.

COMPLETELY ASSEMBLED SINGLE CHANNEL FIGURE 7-1

OPENED-UP SINGLE CHANNEL FIGURE 7-2

COMPLETELY ASSEMBLED SINGLE CHANNEL FIGURE 7-1

OPENED-UP SINGLE CHANNEL FIGURE 7-2

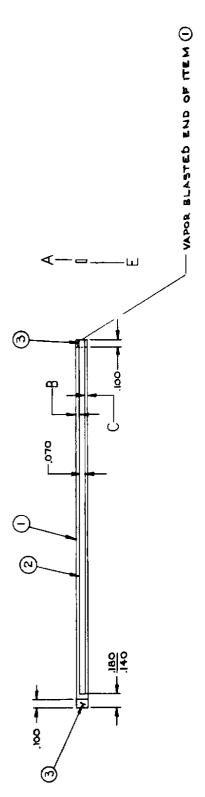

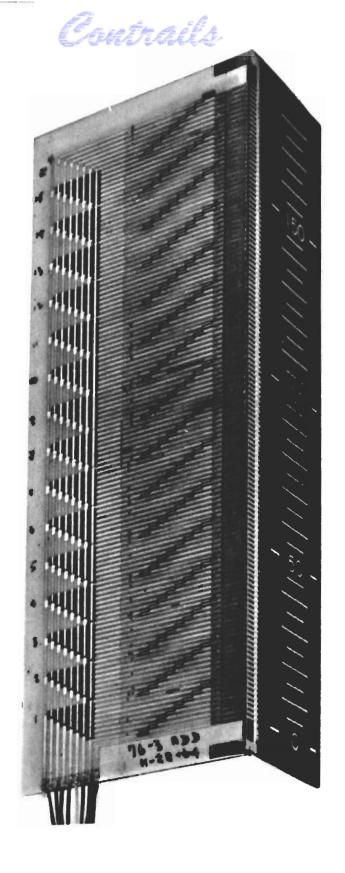

The "front-end" consists of two assemblies of stacked layers cemented together at right angles as shown in Figure 7-3. The electrical interconnect is accomplished by painting 256 (two per display segment) stripes of silver filled epoxy. The pigtail is attached by soldering and supporting with cement. The right angle assembly is then cemented and clamped to the aluminum frame as shown in Figure 7-1.

All interconnect of the major subassemblies is by means of point to point wiring. No internal connectors were used in order to conserve space and increase reliability.

# RIGHT ANGLE CONNECTION - DISPLAY LAMP MATRIX FIGURE 7-3

#### 8 READABILITY OF THE DISPLAY

A significant improvement in the visibility of electroluminescent displays has been demonstrated by the Instrument Division of Lear Siegler, Inc. This process involves the use of a thin-film filter that is an integral part of the EL lamp. Since the filter is a part of the lamp, it is more efficient than conventional filters, such as the honeycomb filter, gray glass, or the lacquer and gelatine filters. The technique provides very high contrast in both color and brightness, between the lighted area and the background.

The diffuse reflectance of the unlighted area of a high contrast lamp is only 2%, while the reflectance of a conventional EL lamp is about 48%. The high contrast absorption filter is located between the transparent front electrode and the phosphor-dielectric layer. Ambient light must enter the glass, pass through the front electrode and contrast filter, then reflect off the phosphor and pass for a second time through the filter and substrate before reaching an observer. Therefore, ambient light is absorbed twice by the contrast filter whereas light emitted from the display is only absorbed once.

Using the following measured transmission and reflectance valves, T=0. 85 (substrate), T=0. 30 (contrast filter), and R=0. 48 (phosphor), a simple calculation reveals that the diffuse reflectance should be 3. 12%.

This technique may be specified by describing the contrast between the lighted and unlighted areas of the display. The contrast ratio shall be greater than 5 to 1 when the EL lamp is excited with its rated voltage and frequency and the display is illuminated with 100 foot-Lamberts of diffused white light. The contrast ratio =  $\frac{B-A}{A}$

where: A = foot-Lambert reading of the unlighted area.

B = foot-Lambert reading of the lighted area.

This ratio shall be maintained over the entire display area, including the area to within 0.025 inch of the lighted area.

Two tests of the effectiveness of this advanced EL display are worthy of note. In one test a high intensity spot light was used to illuminate the surface of the display and a standard numeric. The brightness on the surface of both displays was 1000 foot-Lamberts, as measured with an MgO disc and a Spectra Spot Brightness Meter.

The Hi-Contrast display was plainly visible while the ordinary display was completely washed out. A second test was the demonstration of the same comparison as above, but outside in direct sunlight. The demonstration was held at about 11 AM on a December morning. There was a very slight haze, but shadows were distinct. The Hi-Contrast display was plainly visible with the sunlight directly on the surface. Naturally, the ordinary display was totally unreadable.

Since the filter minimizes reflections within the lamp itself as well, it also makes the display more visible than conventional solid-state displays in dark environments.

Without doubt the high contrast technique developed by the solid-state design engineers of the Instrument Division is a significant improvement in display technology. This advanced application technique has been demonstrated to provide the visibility necessary to use electroluminescent displays in environments of high ambient light.

#### 9 OPERATION OF THE DISPLAY

#### 9.1 RESPONSE TIME

Since the updating time of the input storage register is one cycle per second the minimum time for any change could be as much as 1.7 seconds. This means, however, that in terms of slowing speed the reading could go from zero to full scale in 1.7 seconds. If, however, it was desired to see the change of each segment consecutively, it would require one second per segment and take 128 seconds to go from zero to full scale.

#### 9. 2 TIME DELAYS

While observing the display, certain built-in time delays will be noticeable for certain switching conditions. If the input changes suddenly to indicate a large down-scale change, the topmost address group would go off in approximately 215 msecs. The next hold groups would not go out for approximately 640 msecs. The new address group would have some segments that would go out in approximately 430 msecs. Therefore, it can be seen that the transition downward is not completely uniform during the transient time.

If the input changes such to indicate a large up-scale change, the following events would occur. The hold groups below the top address group will come on with no delay. The top address group will come on after 430 msecs delay. Certain segments of the bottom address group will dim for approximately 200 msecs and then come on full. Here again it can be seen that the transition from a low scale value to a high value is not completely uniform during the transient time.

#### 9.3 TEMPERATURE AND POWER REQUIREMENTS

The maximum power requirements for the indicator can be broken down as follows:

| 208 V AC power               | 24.5 watts  |

|------------------------------|-------------|

| 216 V DC full wave rectified | 24.0 watts  |

| 6 V DC                       | 6.0 watts   |

| Total Power                  | 54. 5 watts |

With 54.5 watts dissipated in the small volume of the indicator, the internal heat rise is quite large. The case temperature measured in a room temperature ambient after power had been applied for 6 hours was approximately 70°C. It is estimated that at some of the heat generating components the temperature would be 100°C. When using the indicator for any length of time, external cooling should be applied to lengthen the life of both the PC's and the EL lamps.

| F 2   | <u></u> | ch.   |

|-------|---------|-------|

| E SEL | ロスクマイス  | REAL. |

| -     | C 0     |       |

| Security Classification                                         | WILLIAM .                                                                     |               |                                      |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------|---------------|--------------------------------------|--|

|                                                                 | NTROL DATA - RAD                                                              |               |                                      |  |

| (Security classification of title, body of abstract and indexi- | ng annotation must be ente                                                    | ered when t   | the overell report is classified)    |  |

| 1. ORIGINATING ACTIVITY (Corporate author)                      | i ·                                                                           |               | T SECURITY CLASSIFICATION CLASSIFIED |  |

| Lear Siegler, Inc., Instrument Division                         |                                                                               |               |                                      |  |

| 41/1 Eastern Avenue, S. E.                                      | ļ*                                                                            | 6 GROUP<br>N/ | Ã                                    |  |

| Grand Rapids, Mich                                              |                                                                               |               |                                      |  |

| A Final Report on Solid State Display                           | Devices                                                                       |               |                                      |  |

| in the port of the port of the property                         | 2012000                                                                       |               |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

| 4. DESCRIPTIVE NOTES (Type of report and inclusive dates)       |                                                                               |               | <del></del>                          |  |

| Final Report - May 1963 to June 1965                            |                                                                               |               |                                      |  |

| 5. AUTHOR(S) (Last name, first name, initial)                   |                                                                               |               |                                      |  |

| VanMinkle, Glenn L.                                             |                                                                               |               |                                      |  |

| DeBono, Mark A.                                                 |                                                                               |               |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

| 6. REPORT DATE                                                  | 7g. TOTAL NO. OF PA                                                           | GES           | 7b. NO. OF REFS                      |  |

| August 1966                                                     | 75                                                                            |               | None                                 |  |

| 8a. CONTRACT OR GRANT NO.                                       | 94 ORIGINATOR'S REF                                                           | PORT NUM      | BER(S)                               |  |

| AF33(657) <b>-11</b> 554                                        |                                                                               | - <b>.</b>    |                                      |  |

| b. PROJECT NO.                                                  | GRR-65-1063                                                                   |               |                                      |  |

| 6190                                                            |                                                                               |               |                                      |  |

| • Task No:                                                      | \$5. OTHER REPORT NO(\$) (Any other numbers that may be seeigned this report) |               |                                      |  |

| 619009                                                          | AFFDL-TR                                                                      |               |                                      |  |

| d.  10. A VAIL ABILITY/LIMITATION NOTICES                       |                                                                               | •             |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

| Distribution of this document is unlir                          | mited.                                                                        |               |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

| 11. SUPPL EMENTARY NOTES                                        | 12. SPONSORING MILIT                                                          | ARY ACT       | VITY                                 |  |

|                                                                 | Air Force Fli                                                                 | ght Dy        | namics Laboratory                    |  |

|                                                                 | Wright-Patter                                                                 | son AF        | B, Ohio                              |  |

|                                                                 |                                                                               |               | _                                    |  |

| 13. ABSTRACT                                                    | ·                                                                             |               |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

| The result of this program was the dev                          |                                                                               |               |                                      |  |

| utilizing binary input information.                             |                                                                               |               |                                      |  |

| the program produced the application of                         |                                                                               |               |                                      |  |

| as many as 128 individual switching e                           |                                                                               |               |                                      |  |

| conductor switches are driven with ele                          |                                                                               |               |                                      |  |

| made up of five columns of segmented                            |                                                                               |               |                                      |  |

| of 32 lines per inch. Four of the co                            |                                                                               |               |                                      |  |

| the fifth is a single line which moves                          | s as a time refe                                                              | erence.       |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

|                                                                 |                                                                               |               |                                      |  |

DD 1508M 1473

UNCLASSIFIED

Security Classification

| 4.                               | LIN  | KA | LINK B |    | LINK C |    |

|----------------------------------|------|----|--------|----|--------|----|

| KEY WORDS                        | ROLE | WΤ | ROLE   | ₩T | ROLE   | ₩T |

| Solid State Displays             |      |    |        |    | ļ      |    |

| Photoconductive Elements         |      |    |        |    |        |    |

| Bargraph Displays                |      |    |        |    |        |    |

| High Contrast Techniques         |      |    |        |    |        |    |

| Electroluminescent Elements      |      |    |        |    |        |    |

| Free morningnescent a prement of |      |    |        |    |        |    |

|                                  |      |    |        |    |        |    |

|                                  |      |    |        |    |        |    |

|                                  |      |    |        |    | }      |    |

|                                  |      |    |        |    |        |    |

|                                  |      |    |        |    |        |    |

|                                  |      |    |        |    |        |    |

|                                  |      |    |        |    |        |    |

|                                  |      |    |        |    | 1      |    |

|                                  |      |    | ]      |    |        |    |

|                                  |      |    |        |    |        |    |

#### INSTRUCTIONS

- 1. ORIGINATING ACTIVITY: Enter the name and address of the contractor, subcontractor, grantee, Department of Defense activity or other organization (corporate author) issuing the report.

- 2a. REPORT SECURITY CLASSIFICATION: Enter the overall security classification of the report. Indicate whether "Restricted Data" is included. Marking is to be in accordance with appropriate security regulations.

- 2b. GROUP: Automatic downgrading is specified in DoD Directive 5200.10 and Armed Forces Industrial Manual. Enter the group number. Also, when applicable, show that optional markings have been used for Group 3 and Group 4 as authorized.

- 3. REPORT TITLE: Enter the complete report title in all capital letters. Titles in all cases should be unclassified. If a meaningful title cannot be selected without classification, show title classification in all capitals in parenthesis immediately following the title.

- 4. DESCRIPTIVE NOTES: If appropriate, enter the type of report, e.g., interim, progress, summary, annual, or final. Give the inclusive dates when a specific reporting period is covered.

- 5. AUTHOR(S): Enter the name(s) of author(s) as shown on or in the report. Enter last name, first name, middle initial. If military, show rank and branch of service. The name of the principal author is an absolute minimum requirement.

- 6. REPORT DATE: Enter the date of the report as day, month, year, or month, year. If more than one date appears on the report, use date of publication.

- 7a. TOTAL NUMBER OF PAGES: The total page count should follow normal pagination procedures, i.e., enter the number of pages containing information.

- 7b. NUMBER OF REFERENCES: Enter the total number of references cited in the report.

- 8a. CONTRACT OR GRANT NUMBER: If appropriate, enter the applicable number of the contract or grant under which the report was written.

- 8b, 8c, & 8d. PROJECT NUMBER: Enter the appropriate military department identification, such as project number, subproject number, system numbers, task number, etc.

- 9a. ORIGINATOR'S REPORT NUMBER(S): Enter the official report number by which the document will be identified and controlled by the originating activity. This number must be unique to this report.

- 9b. OTHER REPORT NUMBER(\$): If the report has been assigned any other report numbers (either by the originator or by the sponsor), also enter this number(s).

- AVAILABILITY/LIMITATION NOTICES: Enter any limitations on further dissemination of the report, other than those

imposed by security classification, using standard statements such as:

- "Qualified requesters may obtain copies of this report from DDC."

- (2) "Foreign announcement and dissemination of this report by DDC is not authorized."

- (3) "U. S. Government agencies may obtain copies of this report directly from DDC. Other qualified DDC users shall request through

- (4) "U. S. military agencies may obtain copies of this report directly from DDC. Other qualified users shall request through

- (5) "All distribution of this report is controlled. Qualified DDC users shall request through

If the report has been furnished to the Office of Technical Services, Department of Commerce, for sale to the public, indicate this fact and enter the price, if known

- 11. SUPPLEMENTARY NOTES: Use for additional explanatory notes.

- 12. SPONSORING MILITARY ACTIVITY: Enter the name of the departmental project office or laboratory sponsoring (paying for) the research and development. Include address.

- 13. ABSTRACT: Enter an abstract giving a brief and factual summary of the document indicative of the report, even though it may also appear elsewhere in the body of the technical report. If additional space is required, a continuation sheet shall be attached.

It is highly desirable that the abstract of classified reports be unclassified. Each paragraph of the abstract shall end with an indication of the military security classification of the information in the paragraph, represented as (TS), (S), (C), or (U).

There is no limitation on the length of the abstract. However, the suggested length is from 150 to 225 words.

14. KEY WORDS: Key words are technically meaningful terms or short phrases that characterize a report and may be used as index entries for cataloging the report. Key words must be selected so that no security classification is required. Identifiers, such as equipment model designation, trade name, military project code name, geographic location, may be used as key words but will be followed by an indication of technical context. The assignment of links, rules, and weights is optional.

GPO 886-551